20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 127

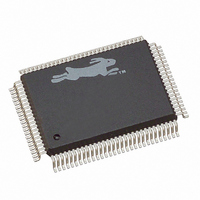

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 127 of 228

- Download datasheet (2Mb)

Table 12-1 lists the serial port registers.

Table 12-2 describes the serial port status registers.

Writing to the status register clears the transmit interrupt request FF, but has no other effect.

Chapter 12 Rabbit Serial Ports

Bit 7—Receiver ready. This bit is set when a byte is transferred from the receiver shift regis-

Bit 6—Address bit or 9th (8th) bit. This bit is set if the character in the receiver data register

Bit 5—This bit is set if the receiver is overrun. This happens if the shift register and the data reg-

Bit 3—Transmitter data buffer full. This bit is set when the transmit data register is full, that

Bit 2—Transmitter busy bit. This bit is set if the transmitter shift register is busy sending

Bits 0,1,4—Always read as zero.

Receiver

ready (there

is a byte in

the receive

data register)

Data Register

Alternate Data Register to

Send 9th (8th) Address Bit

Long Stop Register

Status Register (read, write

to clear transmit IRQ)

Control Register (write only)

* Extra stop bit is supported in revisions A–C of the Rabbit 2000 chip via this register.

Table 12-2. Serial Port Status Registers (adr = 11xx0011, xx = A,B,C,D)

ter to the receiver data register. The bit is cleared when the receiver data register is read.

The transition from "0" to "1" sets the receiver interrupt request flip-flop.

has a 9th (8th) bit. This bit is cleared and should be checked before reading a data register

since a new data value with a new address bit may be loaded immediately when the data

register is read.

ister are full and a start bit is detected. This bit is cleared when the receiver data register is read.

is, a byte is written to the serial port data register. It is cleared when a byte is transferred to

the transmitter shift register or a write operation is performed to the serial port status regis-

ter. This bit will request an interrupt on the transition from 1 to 0 if interrupts are enabled.

data. It is set on the falling edge of the start bit, which is also the clock edge that transfers

data from the transmitter data register to the transmitter shift register. The transmitter busy

bit is cleared at the end of the stop bit of the character sent. This bit will cause an interrupt

to be latched when it goes from busy to not busy status after the last character has been

sent (there are no more data in the transmitter data register).

Bit 7

Register

9th bit

received

Bit 6

*

Table 12-1. Serial Port Registers

Receive

buffer

overrun

Address xx = 00, 01, 10, 11

Bit 5

for A, B, C, D

11xx0000

11xx0001

11xx0010

11xx0011

11xx0100

0

Bit 4

Transmitter

data

register is

full

Bit 3

Mnemonic x = A, B, C, D

Transmitter

is sending a

byte

Bit 2

SxDR

SxAR

SxLR

SxSR

SxCR

0,0

Bit 1,0

121

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: