20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 23

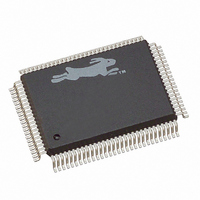

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 23 of 228

- Download datasheet (2Mb)

the root segment or it may contain data variables. The stack segment is normally 4K long

and it holds the system stack. The XPC segment is normally used to execute code that is

not stored in the root segment or the data segment. Special instructions support executing

code that is visible in the XPC segment.

The memory interface unit receives the 20-bit addresses generated by the memory-map-

ping unit. The memory interface unit conditionally modifies address lines A16, A18 and

A19. The other address lines of the 20-bit address are passed unconditionally. The mem-

ory interface unit provides control signals for external memory chips. These interface sig-

nals are chip selects (/CS0, /CS1, /CS2), output enables (/OE0, /OE1), and write enables

(/WE0, /WE1). These signals correspond to the normal control lines found on static mem-

ory chips (chip select or /CS, output enable or /OE, and write enable or /WE). In order to

generate these memory control signals, the 20-bit address space is divided into four quad-

rants of 256K each. A bank control register for each quadrant determines which of the

chip selects and which pair of output enables, and write enables (if any) is enabled when a

memory read or write to that quadrant takes place. For example, if a 512K x 8 flash mem-

ory is to be accessed in the first 512K of the 20-bit address space, then /CS0, /WE0, /OE0

could be enabled in both quadrants.

Figure 3-4 shows a memory interface unit.

Chapter 3 Details on Rabbit Microprocessor Features

Axxin—from processor

Axx—out from memory

Address lines not shown

are passed directly.

control unit

Optional A19 inversion

A19in

Read/Write

Synchronization

A18in

Figure 3-4. Memory Interface Unit

A19in'

A19in

A18in

memory

control

A19

A18

/CS0

/CS1

/CS2

/OE0

/WE0

/OE1

/WE1

A18, A19 invertible

by quadrant

memory

control

lines

17

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: