20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 42

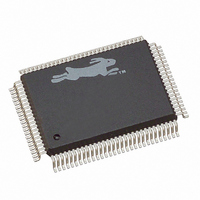

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 42 of 228

- Download datasheet (2Mb)

the same priority, this introduces interrupt latency while the next routine is waiting for the

previous routine to allow more interrupts to take place. If a number of devices have inter-

rupt service routines, and all interrupts are of the same priority, then pending interrupts

can not take place until at least the interrupt service routine in progress is finished, or at

least until it changes the interrupt priority. As a rule of thumb, Rabbit Semiconductor

usually suggests that 100 µs be allowed for interrupt latency on Z180-based controllers.

This can result if, for example, there are five active interrupt routines, and each turns off

the interrupts for at most 20 µs.

The intention in the Rabbit is that most interrupting devices will use priority 1 level inter-

rupts. Devices that need extremely fast response to interrupts will use priority level 2 or 3

interrupts. Since code that runs at priority level 0 or 1 never disables level 2 and level 3

interrupts, these interrupts will take place within about 20 clocks, the length of the longest

instruction or longest sensible sequence of privileged instructions followed by an unprivi-

leged instruction. It is important that the user be careful not to overdisable interrupts in

critical code sections. The processor priority should not be raised above level 1 except in

carefully considered situations.

The effect of the processor priority on interrupts is shown in Table 3-1. The priority of the

interrupt is usually established by bits in an I/O control register associated with the hard-

ware that creates the interrupt. The 8-bit interrupt register (IP) holds the processor priority

in the least significant 2 bits. When an interrupt takes place, the IP register is shifted left 2

positions and the lower 2 bits are set to equal the priority of the interrupt that just took

place. This means that an interrupt service request (ISR) can only be interrupted by an

interrupt of higher priority (unless the priority is explicitly set lower by the programmer).

The IP register serves as a 4-word stack of 2-bit words to save and restore interrupt priori-

ties. It can be shifted right, restoring the previous priority by a special instruction (

Since only the current processor priority and 3 previous priorities can be saved in the inter-

rupt register, instructions are also provided to

new priority can be “pushed” into the IP register with special instructions (

IPSET 1

36

,

IPSET 2

Table 3-1. Effect of Processor Priorities on Interrupts

Processor

Priority

,

0

1

2

3

IPSET 3

All interrupts, priority 1,2 and 3 take place after

execution of current non privileged instruction.

Only interrupts of priority 2 and 3 take place.

Only interrupts of priority 3 take place.

All interrupt are suppressed (except RST instruction).

).

Effect on Interrupts

PUSH

and

Rabbit 2000 Microprocessor User’s Manual

POP IP

using the regular stack. A

IPSET 0

IPRES

,

).

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: