20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 135

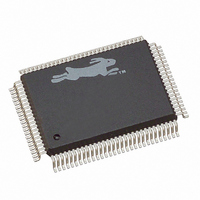

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 135 of 228

- Download datasheet (2Mb)

Figure 12-7 shows the timing relationship among

data receive. Note that RxA is sampled by the rising edge of

When clocking the Rabbit externally, the maximum serial clock frequency is limited by

the amount of time required to synchronize the external clock with the Rabbit

we sum the maximum number of

tion for each of the receive and transmit cases, then the fastest external serial clock fre-

quency would be limited to

12.7 Serial Port Software Suggestions

The receiver and transmitter share the same interrupt vector, but it is possible to make the

receive and transmit interrupt service routines (ISRs) separate by dispatching the interrupt

to either of two different routines. This is desirable to make the ISR less complex and to

reduce the interrupt off time. No interrupts will be lost since distinct interrupt flip-flops

exist for receive and transmit. The dispatcher can test the receiver data register full bit to

dispatch. If this bit is on, the interrupt is dispatched for receive, otherwise for transmit.

The receiver receives first consideration because it must be serviced attentively or data

could be lost.

The dispatcher might look as follows.

The individual interrupts would assume that register AF has been saved and the status reg-

ister has been loaded into register A.

The interrupt service routines can, as a matter of good practice and obtaining optimum

performance, remove the cause of the interrupt and re-enable the interrupts as soon as pos-

sible. This keeps the interrupt latency down and allows the fastest transmission speed on

all serial ports.

All the serial ports will normally generate priority level 1 interrupts. In exceptional circum-

stances, one or more serial ports can be configured to use a higher priority interrupt. There is

Chapter 12 Rabbit Serial Ports

perclk

CLKA

(Ext.)

RxA

interrupt:

PUSH AF

IOI LD A,(SCSR)

OR A

JP M,receive

JP transmit

Figure 12-7. Synchronous Serial Data Receive Timing with External Clock

; 10

; 7 get status register serial port C

; 2 test sign bit

; 7 go service the receive interrupt

; 7 (41 clocks to here) go service transmit interrupt

perclk

perclk

/6.

cycles required to perform clock synchroniza-

perclk

, the external serial clock, and

perclk

.

Valid

perclk

. If

129

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: