20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 43

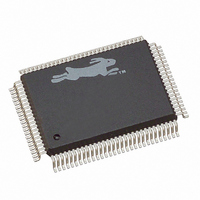

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 43 of 228

- Download datasheet (2Mb)

3.5.2 Multiple External Interrupting Devices

The Rabbit has two distinct external interrupt request lines. If there are more than two

external causes of interrupts, then these lines must be shared between multiple devices.

The interrupt line is edge sensitive, meaning that it requests an interrupt only when a rising

or falling edge, whichever is specified in the setup registers, takes place. The state of the

interrupt line(s) can always be read by reading parallel port E since they share pins with

parallel port E.

If several lines are to share interrupts with the same port, the individual interrupt requests

would normally be or’ed together so that any device can cause an interrupt. If several

devices are requesting an interrupt at the same time, only one interrupt results because

there will be only one transition of the interrupt request line. To resolve the situation and

make sure that the separate interrupt routines for the different devices are called, a good

method is to have a interrupt dispatcher in software that is aided by providing separate

attention request lines for each device. The attention request lines are basically the inter-

rupt request lines for the separate devices before they are or’ed together. The interrupt dis-

patcher calls the interrupt routines for all devices requesting interrupts in priority order so

that all interrupts are serviced.

3.5.3 Privileged Instructions, Critical Sections and Semaphores

Normally an interrupt happens at the end of the instruction currently executing. However,

if the instruction executing is privileged, the interrupt cannot take place at the end of the

instruction and is deferred until a non privileged instruction is executed, usually the next

instruction. Privileged instructions are provided as a handy way of making a certain oper-

ation atomic because there would be a software problem if an interrupt took place after the

instruction. Turning off the interrupts explicitly may be too time consuming or not possi-

ble because the purpose of the privileged instruction is to manipulate the interrupt con-

trols. For additional information on privileged instructions, see Section 18.19, “Privileged

Instructions”

The privileged instructions to load the stack are listed below.

The following instructions to load SP are privileged because they are frequently followed

by an instruction to change the stack segment register. If an interrupt occurs between these

two instructions and the following instruction, the stack will be ill-defined.

Chapter 3 Details on Rabbit Microprocessor Features

LD SP,HL

LD SP,IY

LD SP,IX

LD SP,HL

IOI LD sseg,a

37

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: