20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 91

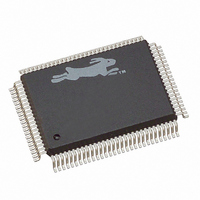

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 91 of 228

- Download datasheet (2Mb)

The interrupts differ from most Z80 or Z180 interrupts in that the 256-byte tables pointed

to EIR and IIR contain the actual instructions beginning the interrupt routines rather than a

16-bit pointer to the routine. The interrupt vectors are spaced 16 bytes apart so that the

entire code will fit in the table for very small interrupt routines.

Interrupts have priority 1, 2 or 3. The processor operates at priority 0, 1, 2 or 3. If an inter-

rupt is being requested, and its priority is higher than the priority of the processor, the

interrupt will take place after then next instruction. The interrupt automatically raises the

processor’s priority to its own priority. The old processor priority is pushed into the 4-

position stack of priorities contained in the IP register. Multiple devices can be requesting

interrupts at the same time. In each case there is a latch set in the device that requests the

interrupt. If that latch is cleared before the interrupt is latched by the central interrupt

logic, then the interrupt request is lost and no interrupt takes place. This is shown in

Table 7-12. The priorities shown in this table apply only for interrupts of the same priority

level and are only meaningful if two interrupts are requested at the same time. Most of the

devices can be programmed to interrupt at priority level 1, 2 or 3.

In the case of the external interrupts the only action that will clear the interrupt request is

for the interrupt to take place, which automatically clears the request. A special action

must be taken in the interrupt service routine for the other interrupts.

Chapter 7 Miscellaneous I/O Functions

Highest

Lowest

Priority

* If the compare registers (TBMxR and TBLxR) are not written within the ISR, the interrupt will

will only be requested once.

Table 7-12. Interrupts—Priority and Action to Clear Requests

Serial Port D

External 1

External 0

Periodic (2 kHz)

Timer B

Timer A

Slave Port

Serial Port A

Serial Port B

Serial Port C

Interrupt Source

Automatically by interrupt acknowledge.

Automatically by interrupt acknowledge.

Read GCSR.

Read TBCSR

Read TACSR.

Write SPSR.

Rx: Read SADR or SAAR.

Tx: Write SADR, SAAR or SASR

Rx: Read SBDR or SBAR.

Tx: Write SBDR, SBAR or SBSR

Rx: Read SCDR or SCAR.

Tx: Write SCDR, SCAR or SCSR

Rx: Read SDDR or SDAR.

Tx: Write SDDR, SDAR or SDSR

Action Required to Clear the Interrupt

*

.

85

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: