20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 41

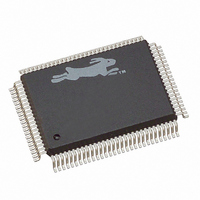

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 41 of 228

- Download datasheet (2Mb)

3.5 Interrupt Structure

When an interrupt occurs on the Rabbit, the return address is pushed on the stack, and con-

trol is transferred to the address of the interrupt service routine. The address of the inter-

rupt service routine has two parts: the upper byte of the address comes from a special

register and the lower byte is fixed by hardware for each interrupt, as shown in Table 7-11.

There are separate registers for internal interrupts (IIR) and external interrupts (EIR) to

specify the high byte of the interrupt service routine address. These registers are accessed

by special instructions.

Interrupts are initiated by hardware devices or by certain 1-byte instructions called reset

instructions.

The

removed from the instruction set (00, 08, 30). The

less of the processor priority. The user is advised to exercise caution when using these

instructions as they are mostly reserved for the use of Dynamic C for debugging. Unlike

the Z80 or Z180, the IIR register contributes the upper byte of the service routine address

for RST interrupts.

Since interrupt routines do not affect the XPC, interrupt routines must be located in the

root code space. However, they can jump to the extended code space after saving the XPC

on the stack.

3.5.1 Interrupt Priority

The Z80 and Z180 have two levels of interrupt priority: maskable and nonmaskable. The

nonmaskable interrupt cannot be disabled and has a fixed interrupt service routine address

of 0x66. The Rabbit, in contrast, has three levels of interrupt priority and four priority lev-

els at which the processor can operate. If an interrupt is requested, and the priority of the

interrupt is higher than that of the processor, the interrupt will take place after the execu-

tion of the current instruction is complete (except for privileged instructions).

Multiple interrupt priorities have been established to make it feasible for the embedded

systems programmer to have extremely fast interrupts available. Interrupt latency refers to

the time required for an interrupt to take place after it has been requested. Generally, inter-

rupts of the same priority are disabled when an interrupt service routine is entered. Some-

times interrupts must stay disabled until the interrupt service routine is completed, other

times the interrupts can be re-enabled once the interrupt service routine has at least dis-

abled its own cause of interrupt. In any case, if several interrupt routines are operating at

Chapter 3 Details on Rabbit Microprocessor Features

RST

LD A,IIR

LD IIR,A

LD A,EIR

LD EIR,A

RST 10

RST 18

RST 20

RST 28

RST 38

instructions are similar to those on the Z80 and Z180, but certain ones have been

RST

interrupts are not inhibited regard-

35

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: