20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 223

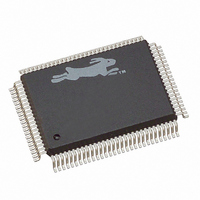

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 223 of 228

- Download datasheet (2Mb)

unless the station is very weak, in which case the interference will be seen as noise distrib-

uted over the screen.

A more important change in timing is that the memory access time will be shortened. The

shortening with the clock doubler enabled and zero wait states is a maximum of 6 ns in the

normal mode and 9 ns in the strong mode. Only one of the 2 clocks in a memory cycle will

be shortened.

Figure B-3. Clock Spectrum Spreader Example

If the clock doubler is not enabled, then the maximum shortening will be 9 ns in the nor-

mal mode and 18 ns in the strong mode. Figure B-3 assumes that the combined address

out and data setup in is 12 ns. The time from clock to output enable is assumed to be 5 ns.

The maximum asymmetry of the clock is assumed to be 52-48%, which shortens one

clock by 4% and lengthens the other by 4% if the clock is doubled.

Early output enable is enabled by default on the Rabbit 2000C, but may be disabled. The

clock low time is controlled by the clock doubler control register, and is assumed to be a

minimum of 14 ns in the above example. Also the maximum clock speed from the exam-

ple with the spreader enabled and 55 ns memory with 25 ns output enable is 25.8 MHz. At

29.49 MHz the memory access must be 50 ns, and the spectrum spreader must be turned

off, or a wait state must be added. Operation with a doubled clock and the spreader

enabled at 29.49 MHz is only allowed for T < 70°C and V > 4.75 V since the instanta-

neous clock frequency bursts to 38.5 MHz when the spectrum spreader and clock asym-

metry together produce maximum shortening of a clock cycle.

Appendix B Rabbit 2000 Revisions

217

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: