UPD78F9212CS-CAB-A Renesas Electronics America, UPD78F9212CS-CAB-A Datasheet - Page 48

UPD78F9212CS-CAB-A

Manufacturer Part Number

UPD78F9212CS-CAB-A

Description

MCU 8BIT 4KB FLASH 16PIN

Manufacturer

Renesas Electronics America

Series

78K0S/Kx1+r

Datasheet

1.UPD78F9510GR-JJG-A.pdf

(364 pages)

Specifications of UPD78F9212CS-CAB-A

Core Processor

78K0S

Core Size

8-Bit

Speed

10MHz

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

13

Program Memory Size

4KB (4K x 8)

Program Memory Type

FLASH

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

2 V ~ 5.5 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Connectivity

-

- Current page: 48 of 364

- Download datasheet (3Mb)

<R>

Notes 1.

Remark For a bit name enclosed in angle brackets (<>), the bit name is defined as a reserved word in the RA78K0S,

46

FFA9H to

FFE1H to

FFE5H to

to FFFFH

to FFF2H

FFF5H to

Address

FFDFH

FFEBH

FFECH

FFEDH

FFFCH

FFA0H

FFA1H

FFA2H

FFA3H

FFA4H

FFA5H

FFA6H

FFA7H

FFA8H

FFE0H

FFE3H

FFE4H

FFF3H

FFF4H

FFFAH

FFFBH

2. The oscillation stabilization time that elapses after release of reset is selected by the option byte. For

PFCMD

PFS

FLPMC

FLCMD

FLAPL

FLAPH

FLAPHC

FLAPLC

FLW

IF0

MK0

INTM0

PPCC

OSTS

PCC

Symbol

and is defined as an sfr variable using the #pragma sfr directive in the CC78K0S.

details, refer to CHAPTER 15 OPTION BYTE.

PD78F921x only

<ADIF>

FLAP7

REG7

<ADM

FLW7

FLAP

Note 1

Note 1

C7

K>

7

0

0

0

0

0

0

0

0

0

PRSEL

FLAP6

<TMIF

<TMM

K010>

REG6

FLW6

FLAP

010>

C6

F4

6

0

0

0

0

0

0

0

0

PRSEL

FLAP5

<TMIF

K000>

REG5

<TMM

FLW5

FLAP

ES11

000>

C5

F3

5

0

0

0

0

0

0

0

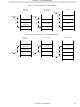

Table 3-3. Special Function Registers (3/3)

PRSEL

FLAP4

<TMIF

<TMM

REG4

FLW4

FLAP

KH1>

ES10

H1>

F2

C4

CHAPTER 3 CPU ARCHITECTURE

4

0

0

0

0

0

0

0

Bit No.

User’s Manual U16994EJ6V0UD

PRSEL

<PIF1> <PIF0> <LVIIF>

FLAP3

REG3

FLW3

<PMK

FLAP

FLAP

ES01

FLA

P11

C11

C3

F1

1>

3

0

0

0

0

0

FLCMD

PRSEL

WEPR

FLAP2

REG2

FLW2

<PMK

FLAP

FLAP

ES00

ERR

FLA

C10

P10

F0

C2

0>

2

2

0

0

0

FLCMD

PPCC1 PPCC0

OSTS1 OSTS0

FLAP1

REG1

PCC1

FLW1

FLAP

FLAP

VCE

<LVI

MK>

FLA

RR

P9

C9

C1

1

0

1

0

FLSPM

FLAP0

REG0

FLCM

FLW0

FLAP

FLAP

FPR

ERR

FLA

D0

P8

C8

C0

0

0

1

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

W

1

Simultaneously

Number of Bits

Manipulated

8

16

Undefined

Undefined

Undefined

Undefined

Note 2

00H

00H

00H

00H

FFH

00H

02H

02H

Reset

After

78, 189

237

237

236

239

240

240

240

240

241

180

181

181

76

76

Related parts for UPD78F9212CS-CAB-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: