MCP1631RD-MCC1 Microchip Technology, MCP1631RD-MCC1 Datasheet - Page 175

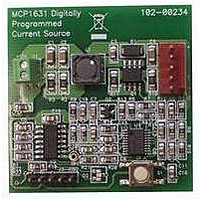

MCP1631RD-MCC1

Manufacturer Part Number

MCP1631RD-MCC1

Description

REFERENCE DESIGN FOR MCP1631HV

Manufacturer

Microchip Technology

Type

Battery Managementr

Datasheets

1.MCP1631VHVT-330EST.pdf

(34 pages)

2.MCP1631HV-330EST.pdf

(54 pages)

3.MCP1631RD-MCC2.pdf

(20 pages)

4.MCP1631RD-MCC2.pdf

(328 pages)

5.MCP1631RD-MCC1.pdf

(28 pages)

Specifications of MCP1631RD-MCC1

Main Purpose

Power Management, Battery Charger

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP1631HV, PIC16F883

Primary Attributes

1 ~ 2 Cell- Li-Ion, 1 ~ 4 Cell- NiCd/NiMH

Secondary Attributes

Status LEDs

Supported Devices

MCP1631HV, PIC16F883 Device Type

Tool / Board Applications

Power Management-Battery Management

Development Tool Type

Reference Design

Input Voltage

5.5 V to 16 V

Product

Power Management Modules

Mcu Supported Families

MCP1631HV/PIC16F883 Family

Silicon Manufacturer

Microchip

Silicon Core Number

MCP1631HV

Kit Application Type

Reference Design

Application Sub Type

Battery Charger

Kit Contents

Board Only

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

MCP1631HV, PIC16F883

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- MCP1631VHVT-330EST PDF datasheet

- MCP1631HV-330EST PDF datasheet #2

- MCP1631RD-MCC2 PDF datasheet #3

- MCP1631RD-MCC2 PDF datasheet #4

- MCP1631RD-MCC1 PDF datasheet #5

- Current page: 175 of 328

- Download datasheet (6Mb)

12.4.1.5

Data is received at the RX/DT pin. The RX/DT pin

output driver is automatically disabled when the

EUSART is configured for synchronous master receive

operation.

In Synchronous mode, reception is enabled by setting

either the Single Receive Enable bit (SREN of the

RCSTA register) or the Continuous Receive Enable bit

(CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many

clock cycles are generated as there are data bits in a

single character. The SREN bit is automatically cleared

at the completion of one character. When CREN is set,

clocks are continuously generated until CREN is

cleared. If CREN is cleared in the middle of a character

the CK clock stops immediately and the partial charac-

ter is discarded. If SREN and CREN are both set, then

SREN is cleared at the completion of the first character

and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is

sampled at the RX/DT pin on the trailing edge of the

TX/CK clock pin and is shifted into the Receive Shift

Register (RSR). When a complete character is

received into the RSR, the RCIF bit is set and the char-

acter is automatically transferred to the two character

receive FIFO. The Least Significant eight bits of the top

character in the receive FIFO are available in RCREG.

The RCIF bit remains set as long as there are un-read

characters in the receive FIFO.

12.4.1.6

Synchronous data transfers use a separate clock line,

which is synchronous with the data. A device configured

as a slave receives the clock on the TX/CK line. The TX/

CK pin output driver is automatically disabled when the

device is configured for synchronous slave transmit or

receive operation. Serial data bits change on the leading

edge to ensure they are valid at the trailing edge of each

clock. One data bit is transferred for each clock cycle.

Only as many clock cycles should be received as there

are data bits.

12.4.1.7

The receive FIFO buffer can hold two characters. An

overrun error will be generated if a third character, in its

entirety, is received before RCREG is read to access

the FIFO. When this happens the OERR bit of the

RCSTA register is set. Previous data in the FIFO will

not be overwritten. The two characters in the FIFO

buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit

can only be cleared by clearing the overrun condition.

If the overrun error occurred when the SREN bit is set

and CREN is clear then the error is cleared by reading

RCREG. If the overrun occurred when the CREN bit is

© 2009 Microchip Technology Inc.

Synchronous Master Reception

Slave Clock

Receive Overrun Error

PIC16F882/883/884/886/887

set then the error condition is cleared by either clearing

the CREN bit of the RCSTA register or by clearing the

SPEN bit which resets the EUSART.

12.4.1.8

The EUSART supports 9-bit character reception. When

the RX9 bit of the RCSTA register is set the EUSART

will shift 9-bits into the RSR for each character

received. The RX9D bit of the RCSTA register is the

ninth, and Most Significant, data bit of the top unread

character in the receive FIFO. When reading 9-bit data

from the receive FIFO buffer, the RX9D data bit must

be read before reading the 8 Least Significant bits from

the RCREG.

12.4.1.9

1.

2.

3.

4.

5.

6.

7.

8.

9.

10. If an overrun error occurs, clear the error by

Initialize the SPBRGH, SPBRG register pair for

the appropriate baud rate. Set or clear the

BRGH and BRG16 bits, as required, to achieve

the desired baud rate.

Enable the synchronous master serial port by

setting bits SYNC, SPEN and CSRC.

Ensure bits CREN and SREN are clear.

If interrupts are desired, set the RCIE bit of the

PIE1 register and the GIE and PEIE bits of the

INTCON register.

If 9-bit reception is desired, set bit RX9.

Start reception by setting the SREN bit or for

continuous reception, set the CREN bit.

Interrupt flag bit RCIF will be set when reception

of a character is complete. An interrupt will be

generated if the enable bit RCIE was set.

Read the RCSTA register to get the ninth bit (if

enabled) and determine if any error occurred

during reception.

Read the 8-bit received data by reading the

RCREG register.

either clearing the CREN bit of the RCSTA

register or by clearing the SPEN bit which resets

the EUSART.

Receiving 9-bit Characters

Synchronous Master Reception Set-

up:

DS41291F-page 173

Related parts for MCP1631RD-MCC1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

REFERENCE DESIGN MCP1631HV

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

REF DES BATT CHARG OR LED DRIVER

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: