MCP1631RD-MCC1 Microchip Technology, MCP1631RD-MCC1 Datasheet - Page 210

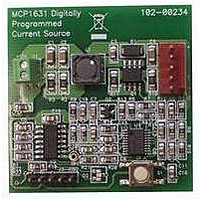

MCP1631RD-MCC1

Manufacturer Part Number

MCP1631RD-MCC1

Description

REFERENCE DESIGN FOR MCP1631HV

Manufacturer

Microchip Technology

Type

Battery Managementr

Datasheets

1.MCP1631VHVT-330EST.pdf

(34 pages)

2.MCP1631HV-330EST.pdf

(54 pages)

3.MCP1631RD-MCC2.pdf

(20 pages)

4.MCP1631RD-MCC2.pdf

(328 pages)

5.MCP1631RD-MCC1.pdf

(28 pages)

Specifications of MCP1631RD-MCC1

Main Purpose

Power Management, Battery Charger

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP1631HV, PIC16F883

Primary Attributes

1 ~ 2 Cell- Li-Ion, 1 ~ 4 Cell- NiCd/NiMH

Secondary Attributes

Status LEDs

Supported Devices

MCP1631HV, PIC16F883 Device Type

Tool / Board Applications

Power Management-Battery Management

Development Tool Type

Reference Design

Input Voltage

5.5 V to 16 V

Product

Power Management Modules

Mcu Supported Families

MCP1631HV/PIC16F883 Family

Silicon Manufacturer

Microchip

Silicon Core Number

MCP1631HV

Kit Application Type

Reference Design

Application Sub Type

Battery Charger

Kit Contents

Board Only

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

MCP1631HV, PIC16F883

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- MCP1631VHVT-330EST PDF datasheet

- MCP1631HV-330EST PDF datasheet #2

- MCP1631RD-MCC2 PDF datasheet #3

- MCP1631RD-MCC2 PDF datasheet #4

- MCP1631RD-MCC1 PDF datasheet #5

- Current page: 210 of 328

- Download datasheet (6Mb)

PIC16F882/883/884/886/887

13.4.17

An SSP Mask (SSPMSK) register is available in I

Slave mode as a mask for the value held in the

SSPSR register during an address comparison

operation. A zero (‘0’) bit in the SSPMSK register has

the effect of making the corresponding bit in the

SSPSR register a “don’t care”.

This register is reset to all ‘1’s upon any Reset

condition and, therefore, has no effect on standard

SSP operation until written with a mask value.

REGISTER 13-4:

DS41291F-page 208

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7-1

bit 0

Note 1: When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed

R/W-1

MSK7

2: In all other SSP modes, this bit has no effect.

SSP MASK REGISTER

through the SSPMSK register.

MSK<7:1>: Mask bits

1 = The received address bit n is compared to SSPADD<n> to detect I

0 = The received address bit n is not used to detect I

MSK<0>: Mask bit for I

I

1 = The received address bit 0 is compared to SSPADD<0> to detect I

0 = The received address bit 0 is not used to detect I

2

C Slave mode, 10-bit Address (SSPM<3:0> = 0111):

R/W-1

MSK6

SSPMSK: SSP MASK REGISTER

W = Writable bit

‘1’ = Bit is set

R/W-1

MSK5

2

C Slave mode, 10-bit Address

R/W-1

MSK4

2

C

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

(1)

R/W-1

MSK3

This register must be initiated prior to setting

SSPM<3:0> bits to select the I

10-bit address).

This register can only be accessed when the appropriate

mode is selected by bits (SSPM<3:0> of SSPCON).

The SSP Mask register is active during:

• 7-bit Address mode: address compare of A<7:1>.

• 10-bit Address mode: address compare of A<7:0>

only. The SSP mask has no effect during the

reception of the first (high) byte of the address.

2

2

C address match

(2)

C address match

R/W-1

MSK2

© 2009 Microchip Technology Inc.

2

2

C address match

C address match

x = Bit is unknown

R/W-1

MSK1

2

C Slave mode (7-bit or

MSK0

R/W-1

(2)

bit 0

Related parts for MCP1631RD-MCC1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

REFERENCE DESIGN MCP1631HV

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

REF DES BATT CHARG OR LED DRIVER

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: