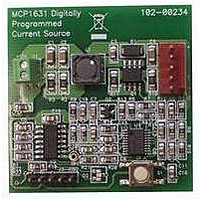

MCP1631RD-MCC1 Microchip Technology, MCP1631RD-MCC1 Datasheet - Page 222

MCP1631RD-MCC1

Manufacturer Part Number

MCP1631RD-MCC1

Description

REFERENCE DESIGN FOR MCP1631HV

Manufacturer

Microchip Technology

Type

Battery Managementr

Datasheets

1.MCP1631VHVT-330EST.pdf

(34 pages)

2.MCP1631HV-330EST.pdf

(54 pages)

3.MCP1631RD-MCC2.pdf

(20 pages)

4.MCP1631RD-MCC2.pdf

(328 pages)

5.MCP1631RD-MCC1.pdf

(28 pages)

Specifications of MCP1631RD-MCC1

Main Purpose

Power Management, Battery Charger

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP1631HV, PIC16F883

Primary Attributes

1 ~ 2 Cell- Li-Ion, 1 ~ 4 Cell- NiCd/NiMH

Secondary Attributes

Status LEDs

Supported Devices

MCP1631HV, PIC16F883 Device Type

Tool / Board Applications

Power Management-Battery Management

Development Tool Type

Reference Design

Input Voltage

5.5 V to 16 V

Product

Power Management Modules

Mcu Supported Families

MCP1631HV/PIC16F883 Family

Silicon Manufacturer

Microchip

Silicon Core Number

MCP1631HV

Kit Application Type

Reference Design

Application Sub Type

Battery Charger

Kit Contents

Board Only

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

MCP1631HV, PIC16F883

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- MCP1631VHVT-330EST PDF datasheet

- MCP1631HV-330EST PDF datasheet #2

- MCP1631RD-MCC2 PDF datasheet #3

- MCP1631RD-MCC2 PDF datasheet #4

- MCP1631RD-MCC1 PDF datasheet #5

- Current page: 222 of 328

- Download datasheet (6Mb)

PIC16F882/883/884/886/887

14.3

The

interrupt sources:

• External Interrupt RB0/INT

• Timer0 Overflow Interrupt

• PORTB Change Interrupts

• 2 Comparator Interrupts

• A/D Interrupt

• Timer1 Overflow Interrupt

• Timer2 Match Interrupt

• EEPROM Data Write Interrupt

• Fail-Safe Clock Monitor Interrupt

• Enhanced CCP Interrupt

• EUSART Receive and Transmit Interrupts

• Ultra Low-Power Wake-up Interrupt

• MSSP Interrupt

The Interrupt Control register (INTCON) and Peripheral

Interrupt Request Register 1 (PIR1) record individual

interrupt requests in flag bits. The INTCON register

also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>),

enables (if set) all unmasked interrupts, or disables (if

cleared) all interrupts. Individual interrupts can be

disabled through their corresponding enable bits in the

INTCON, PIE1 and PIE2 registers, respectively. GIE is

cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits

the interrupt routine, as well as sets the GIE bit, which

re-enables unmasked interrupts.

The following interrupt flags are contained in the INT-

CON register:

• INT Pin Interrupt

• PORTB Change Interrupts

• Timer0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1

and PIR2 registers. The corresponding interrupt enable

bits are contained in PIE1 and PIE2 registers.

The following interrupt flags are contained in the PIR1

register:

• A/D Interrupt

• EUSART Receive and Transmit Interrupts

• Timer1 Overflow Interrupt

• Synchronous Serial Port (SSP) Interrupt

• Enhanced CCP1 Interrupt

• Timer1 Overflow Interrupt

• Timer2 Match Interrupt

DS41291F-page 220

PIC16F882/883/884/886/887

Interrupts

has

multiple

The following interrupt flags are contained in the PIR2

register:

• Fail-Safe Clock Monitor Interrupt

• 2 Comparator Interrupts

• EEPROM Data Write Interrupt

• Ultra Low-Power Wake-up Interrupt

• CCP2 Interrupt

When an interrupt is serviced:

• The GIE is cleared to disable any further interrupt.

• The return address is pushed onto the stack.

• The PC is loaded with 0004h.

For external interrupt events, such as the INT pin,

PORTB change interrupts, the interrupt latency will be

three or four instruction cycles. The exact latency

depends upon when the interrupt event occurs (see

Figure 14-8). The latency is the same for one or

two-cycle instructions. Once in the Interrupt Service

Routine, the source(s) of the interrupt can be

determined by polling the interrupt flag bits. The

interrupt flag bit(s) must be cleared in software before

re-enabling interrupts to avoid multiple interrupt

requests.

For

comparators, A/D, data EEPROM, EUSART, MSSP or

Enhanced CCP modules, refer to the respective

peripheral section.

14.3.1

External interrupt on RB0/INT pin is edge-triggered;

either rising if the INTEDG bit (OPTION_REG<6>) is

set, or falling, if the INTEDG bit is clear. When a valid

edge appears on the RB0/INT pin, the INTF bit

(INTCON<1>) is set. This interrupt can be disabled by

clearing the INTE control bit (INTCON<4>). The INTF

bit must be cleared in software in the Interrupt Service

Routine before re-enabling this interrupt. The RB0/INT

interrupt can wake-up the processor from Sleep, if the

INTE bit was set prior to going into Sleep. The status of

the GIE bit decides whether or not the processor

branches to the interrupt vector following wake-up

(0004h). See Section 14.6 “Power-Down Mode

(Sleep)” for details on Sleep and Figure 14-10 for

timing of wake-up from Sleep through RB0/INT

interrupt.

Note 1: Individual interrupt flag bits are set,

additional

2: When an instruction that clears the GIE

RB0/INT INTERRUPT

regardless

corresponding mask bit or the GIE bit.

bit is executed, any interrupts that were

pending for execution in the next cycle

are ignored. The interrupts, which were

ignored, are still pending to be serviced

when the GIE bit is set again.

information

© 2009 Microchip Technology Inc.

of

the

on

status

Timer1,

of

Timer2,

their

Related parts for MCP1631RD-MCC1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

REFERENCE DESIGN MCP1631HV

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

REF DES BATT CHARG OR LED DRIVER

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: