MCP1631RD-MCC1 Microchip Technology, MCP1631RD-MCC1 Datasheet - Page 34

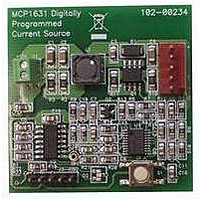

MCP1631RD-MCC1

Manufacturer Part Number

MCP1631RD-MCC1

Description

REFERENCE DESIGN FOR MCP1631HV

Manufacturer

Microchip Technology

Type

Battery Managementr

Datasheets

1.MCP1631VHVT-330EST.pdf

(34 pages)

2.MCP1631HV-330EST.pdf

(54 pages)

3.MCP1631RD-MCC2.pdf

(20 pages)

4.MCP1631RD-MCC2.pdf

(328 pages)

5.MCP1631RD-MCC1.pdf

(28 pages)

Specifications of MCP1631RD-MCC1

Main Purpose

Power Management, Battery Charger

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP1631HV, PIC16F883

Primary Attributes

1 ~ 2 Cell- Li-Ion, 1 ~ 4 Cell- NiCd/NiMH

Secondary Attributes

Status LEDs

Supported Devices

MCP1631HV, PIC16F883 Device Type

Tool / Board Applications

Power Management-Battery Management

Development Tool Type

Reference Design

Input Voltage

5.5 V to 16 V

Product

Power Management Modules

Mcu Supported Families

MCP1631HV/PIC16F883 Family

Silicon Manufacturer

Microchip

Silicon Core Number

MCP1631HV

Kit Application Type

Reference Design

Application Sub Type

Battery Charger

Kit Contents

Board Only

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

MCP1631HV, PIC16F883

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- MCP1631VHVT-330EST PDF datasheet

- MCP1631HV-330EST PDF datasheet #2

- MCP1631RD-MCC2 PDF datasheet #3

- MCP1631RD-MCC2 PDF datasheet #4

- MCP1631RD-MCC1 PDF datasheet #5

- Current page: 34 of 328

- Download datasheet (6Mb)

PIC16F882/883/884/886/887

2.2.2.4

The PIE1 register contains the interrupt enable bits, as

shown in Register 2-4.

REGISTER 2-4:

DS41291F-page 32

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

U-0

—

PIE1 Register

Unimplemented: Read as ‘0’

ADIE: A/D Converter (ADC) Interrupt Enable bit

1 = Enables the ADC interrupt

0 = Disables the ADC interrupt

RCIE: EUSART Receive Interrupt Enable bit

1 = Enables the EUSART receive interrupt

0 = Disables the EUSART receive interrupt

TXIE: EUSART Transmit Interrupt Enable bit

1 = Enables the EUSART transmit interrupt

0 = Disables the EUSART transmit interrupt

SSPIE: Master Synchronous Serial Port (MSSP) Interrupt Enable bit

1 = Enables the MSSP interrupt

0 = Disables the MSSP interrupt

CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

TMR2IE: Timer2 to PR2 Match Interrupt Enable bit

1 = Enables the Timer2 to PR2 match interrupt

0 = Disables the Timer2 to PR2 match interrupt

TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt

0 = Disables the Timer1 overflow interrupt

R/W-0

ADIE

PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

W = Writable bit

‘1’ = Bit is set

R/W-0

RCIE

R/W-0

TXIE

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

SSPIE

R/W-0

Note:

Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

CCP1IE

R/W-0

© 2009 Microchip Technology Inc.

x = Bit is unknown

TMR2IE

R/W-0

TMR1IE

R/W-0

bit 0

Related parts for MCP1631RD-MCC1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

REFERENCE DESIGN MCP1631HV

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

REF DES BATT CHARG OR LED DRIVER

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: