MCP1631RD-MCC1 Microchip Technology, MCP1631RD-MCC1 Datasheet - Page 186

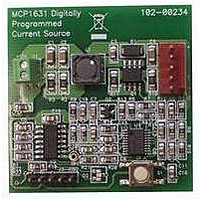

MCP1631RD-MCC1

Manufacturer Part Number

MCP1631RD-MCC1

Description

REFERENCE DESIGN FOR MCP1631HV

Manufacturer

Microchip Technology

Type

Battery Managementr

Datasheets

1.MCP1631VHVT-330EST.pdf

(34 pages)

2.MCP1631HV-330EST.pdf

(54 pages)

3.MCP1631RD-MCC2.pdf

(20 pages)

4.MCP1631RD-MCC2.pdf

(328 pages)

5.MCP1631RD-MCC1.pdf

(28 pages)

Specifications of MCP1631RD-MCC1

Main Purpose

Power Management, Battery Charger

Embedded

Yes, MCU, 8-Bit

Utilized Ic / Part

MCP1631HV, PIC16F883

Primary Attributes

1 ~ 2 Cell- Li-Ion, 1 ~ 4 Cell- NiCd/NiMH

Secondary Attributes

Status LEDs

Supported Devices

MCP1631HV, PIC16F883 Device Type

Tool / Board Applications

Power Management-Battery Management

Development Tool Type

Reference Design

Input Voltage

5.5 V to 16 V

Product

Power Management Modules

Mcu Supported Families

MCP1631HV/PIC16F883 Family

Silicon Manufacturer

Microchip

Silicon Core Number

MCP1631HV

Kit Application Type

Reference Design

Application Sub Type

Battery Charger

Kit Contents

Board Only

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

MCP1631HV, PIC16F883

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- MCP1631VHVT-330EST PDF datasheet

- MCP1631HV-330EST PDF datasheet #2

- MCP1631RD-MCC2 PDF datasheet #3

- MCP1631RD-MCC2 PDF datasheet #4

- MCP1631RD-MCC1 PDF datasheet #5

- Current page: 186 of 328

- Download datasheet (6Mb)

PIC16F882/883/884/886/887

When the application software is expecting to receive

valid data, the SSPBUF should be read before the next

byte of data to transfer is written to the SSPBUF. The

buffer full bit BF of the SSPSTAT register indicates

when SSPBUF has been loaded with the received data

(transmission is complete). When the SSPBUF is read,

the BF bit is cleared. This data may be irrelevant if the

SPI is only a transmitter. Generally, the MSSP Interrupt

is used to determine when the transmission/reception

has completed. The SSPBUF must be read and/or

written. If the interrupt method is not going to be used,

then software polling can be done to ensure that a write

collision does not occur. Example 13-1 shows the

loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable, and

can only be accessed by addressing the SSPBUF

register. Additionally, the MSSP STATUS register

(SSPSTAT register) indicates the various status

conditions.

EXAMPLE 13-1:

DS41291F-page 184

LOOP BTFSS SSPSTAT, BF

GOTO

MOVF

MOVWF RXDATA

MOVF

MOVWF SSPBUF

LOOP

SSPBUF, W

TXDATA, W

LOADING THE SSPBUF (SSPSR) REGISTER

;Has data been received (transmit complete)?

;No

;WREG reg = contents of SSPBUF

;Save in user RAM, if data is meaningful

;W reg = contents of TXDATA

;New data to xmit

13.3.2

To enable the serial port, SSP Enable bit SSPEN of the

SSPCON register must be set. To reset or reconfigure

SPI mode, clear the SSPEN bit, re-initialize the

SSPCON registers, and then set the SSPEN bit. This

configures the SDI, SDO, SCK and SS pins as serial

port pins. For the pins to behave as the serial port

function, some must have their data direction bits (in

the TRIS register) appropriately programmed. That is:

• SDI is automatically controlled by the SPI module

• SDO must have TRISC<5> bit cleared

• SCK (Master mode) must have TRISC<3> bit

• SCK (Slave mode) must have TRISC<3> bit set

• SS must have TRISA<5> bit set

Any serial port function that is not desired may be

overridden by programming the corresponding data

direction (TRIS) register to the opposite value.

cleared

ENABLING SPI I/O

© 2009 Microchip Technology Inc.

Related parts for MCP1631RD-MCC1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

REFERENCE DESIGN MCP1631HV

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

REF DES BATT CHARG OR LED DRIVER

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: