AT91RM3400-DK Atmel, AT91RM3400-DK Datasheet - Page 360

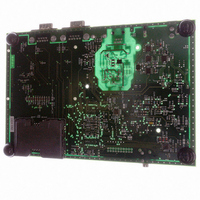

AT91RM3400-DK

Manufacturer Part Number

AT91RM3400-DK

Description

KIT DEV FOR AT91RM3400

Manufacturer

Atmel

Series

AT91SAM Smart ARMr

Type

MCUr

Datasheets

1.AT91RM3400-DK.pdf

(461 pages)

2.AT91RM3400-DK.pdf

(2 pages)

3.AT91RM3400-DK.pdf

(25 pages)

Specifications of AT91RM3400-DK

Contents

Evaluation Board, Software and Documentation

Processor To Be Evaluated

AT91RM3400

Data Bus Width

32 bit

Interface Type

RS-232, USB

For Use With/related Products

AT91RM3400

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 360 of 461

- Download datasheet (6Mb)

TC Channel Mode Register: Capture Mode

Register Name: TC_CMR

Access Type:

• TCCLKS: Clock Selection

• CLKI: Clock Invert

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

• BURST: Burst Signal Selection

• LDBSTOP: Counter Clock Stopped with RB Loading

0 = Counter clock is not stopped when RB loading occurs.

1 = Counter clock is stopped when RB loading occurs.

• LDBDIS: Counter Clock Disable with RB Loading

0 = Counter clock is not disabled when RB loading occurs.

1 = Counter clock is disabled when RB loading occurs.

360

WAVE = 0

LDBDIS

31

23

15

–

–

7

0

0

0

0

1

1

1

1

0

0

1

1

AT91RM3400

BURST

Read/Write

LDBSTOP

CPCTRG

TCCLKS

30

22

14

–

–

6

0

0

1

1

0

0

1

1

0

1

0

1

The clock is not gated by an external signal.

XC0 is ANDed with the selected clock.

XC1 is ANDed with the selected clock.

XC2 is ANDed with the selected clock.

29

21

13

–

–

–

5

0

1

0

1

0

1

0

1

BURST

Clock Selected

TIMER_CLOCK1

TIMER_CLOCK2

TIMER_CLOCK3

TIMER_CLOCK4

TIMER_CLOCK5

XC0

XC1

XC2

28

20

12

–

–

–

4

CLKI

27

19

11

–

–

3

LDRB

ABETRG

26

18

10

–

2

TCCLKS

25

17

–

9

1

ETRGEDG

LDRA

1790A–ATARM–11/03

24

16

–

8

0

Related parts for AT91RM3400-DK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: