AT91RM3400-DK Atmel, AT91RM3400-DK Datasheet - Page 81

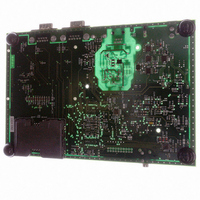

AT91RM3400-DK

Manufacturer Part Number

AT91RM3400-DK

Description

KIT DEV FOR AT91RM3400

Manufacturer

Atmel

Series

AT91SAM Smart ARMr

Type

MCUr

Datasheets

1.AT91RM3400-DK.pdf

(461 pages)

2.AT91RM3400-DK.pdf

(2 pages)

3.AT91RM3400-DK.pdf

(25 pages)

Specifications of AT91RM3400-DK

Contents

Evaluation Board, Software and Documentation

Processor To Be Evaluated

AT91RM3400

Data Bus Width

32 bit

Interface Type

RS-232, USB

For Use With/related Products

AT91RM3400

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 81 of 461

- Download datasheet (6Mb)

Functional Description

Bus Arbiter

Address Decoder

1790A–ATARM–11/03

The Memory Controller handles the internal ASB bus and arbitrates the accesses of

both masters.

It is made up of:

•

•

•

•

•

The MC handles only little-endian mode accesses. The masters work in little-endian

mode only.

The Memory Controller has a simple, hard-wired priority bus arbiter that gives the con-

trol of the bus to one of the two masters. The Peripheral Data Controller has the highest

priority; the ARM processor has the lowest one.

The Memory Controller features an Address Decoder that first decodes the four highest

bits of the 32-bit address bus and defines three separate areas:

•

•

•

Figure 22 shows the assignment of the 256-Mbyte memory areas.

Figure 22. Memory Areas

A bus arbiter

An address decoder

An abort status

A misalignment detector

A memory protection unit

One 256-Mbyte address space for the internal memories

One 256-Mbyte address space reserved for the embedded peripherals

An undefined address space of 3584M bytes representing fourteen 256-Mbyte

areas that return an Abort if accessed

14 x 256MBytes

256M Bytes

256M Bytes

3,584 Mbytes

0x0000 0000

0xF000 0000

0x0FFF FFFF

0xEFFF FFFF

0xFFFF FFFF

0x1000 0000

Internal Memories

Peripherals

Undefined

(Abort)

AT91RM3400

81

Related parts for AT91RM3400-DK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: