TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 128

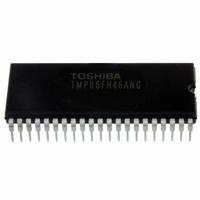

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

- Current page: 128 of 214

- Download datasheet (3Mb)

10.3 Function

SIOCR1<SIOS>

SIOSR<SIOF>

SIOSR<SEF>

SCK

SI pin

SIOSR<RXF>

INTSIO

interrupt

request

SIORDB

pin

Figure 10-11 Example of External Clock and MSB Receive Mode

(4)

the received data is ignored while the SIOSR<RXERR> is “1”.

Receive error processing

Receive errors occur on the following situation. To protect SIORDB and the shift register contents,

• Shift operation is finished before reading out received data from SIORDB at SIOSR<RXF>

is “1” in an external clock operation.

If receive error occurs, set the SIOCR1<SIOS> to “0” for reading the data that received

immediately before error occurence. And read the data from SIORDB. Data in shift register

(at errors occur) can be read by reading the SIORDB again.

When SIOSR<RXERR> is cleared to “0” after reading the received data, SIOSR<RXF> is

cleared to “0”.

After clearing SIOCR1<SIOS> to “0”, when 8-bit serial clock is input to

operation is stopped. To restart the receive operation, confirm that SIOSR<SIOF> is cleared

to “0”.

If the receive error occurs, set the SIOCR1<SIOINH> to “1” for stopping the receive opera-

tion immediately. In this case, SIOCR1<SIOS>, SIOSR register, SIORDB register and

SIOTDB register are initialized.

A7 A6

Start shift

operation

A5 A4 A3 A2 A1 A0 B7 B6 B5 B4 B3 B2 B1 B0 C7 C6 C5 C4 C3 C2 C1 C0

Writing transmit

data A

Reading received data

A

Page 114

Start shift

operation

B

Start shift

operation

Writing transmit

data B

Clearing SIOS

Writing transmit

data C

C

TMP86FH46ANG

SCK

pin, receive

Related parts for TMP86FH46ANG(Z)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: