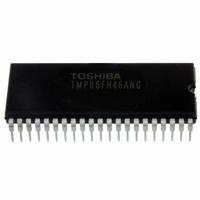

TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 9

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

2. Operational Description

3. Interrupt Control Circuit

Difference among product (TMP86xx46 Series)

TMP86FH46ANG

1.1

1.2

1.3

1.4

2.1

2.2

2.3

3.1

3.2

3.3

3.4

2.1.1

2.1.2

2.1.3

2.2.1

2.2.2

2.2.3

2.2.4

2.3.1

2.3.2

2.3.3

2.3.4

3.2.1

3.2.2

3.4.1

3.4.2

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Pin Names and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

CPU Core Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

System Clock Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2.2.1

2.2.2.2

2.2.3.1

2.2.3.2

2.2.3.3

2.2.4.1

2.2.4.2

2.2.4.3

2.2.4.4

Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Interrupt latches (IL15 to IL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Interrupt enable register (EIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Interrupt Source Selector (INTSEL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Interrupt Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.4.2.1

Memory Address Map............................................................................................................................... 7

Program Memory (Flash) .......................................................................................................................... 7

Data Memory (RAM) ................................................................................................................................. 7

Clock Generator........................................................................................................................................ 8

Timing Generator .................................................................................................................................... 10

Operation Mode Control Circuit .............................................................................................................. 11

Operating Mode Control ......................................................................................................................... 16

External Reset Input ............................................................................................................................... 29

Address trap reset .................................................................................................................................. 30

Watchdog timer reset.............................................................................................................................. 30

System clock reset.................................................................................................................................. 30

Interrupt master enable flag (IMF) .......................................................................................................... 34

Individual interrupt enable flags (EF15 to EF4) ...................................................................................... 34

Interrupt acceptance processing is packaged as follows........................................................................ 37

Saving/restoring general-purpose registers ............................................................................................ 38

Configuration of timing generator

Machine cycle

Single-clock mode

Dual-clock mode

STOP mode

STOP mode

IDLE1/2 mode and SLEEP1/2 mode

IDLE0 and SLEEP0 modes (IDLE0, SLEEP0)

SLOW mode

Using PUSH and POP instructions

Table of Contents

i