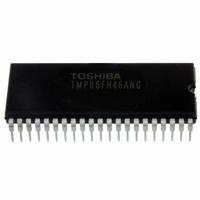

TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 52

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

- Current page: 52 of 214

- Download datasheet (3Mb)

3.4 Interrupt Sequence

Interrupt

request

Interrupt

latch (IL)

IMF

Execute

instruction

PC

SP

3.4.2 Saving/restoring general-purpose registers

Note 1: a: Return address entry address, b: Entry address, c: Address which RETI instruction is stored

Note 2: On condition that interrupt is enabled, it takes 38/fc [s] or 38/fs [s] at maximum (If the interrupt latch is set at the first

1-machine cycle

Figure 3-1 Timing Chart of Interrupt Acceptance/Return Interrupt Instruction

service program

level of current servicing interrupt is requested.

acceptable interrupt sources are selectively enabled by the individual interrupt enable flags.

before setting IMF to “1”. As for non-maskable interrupt, keep interrupt service shorten compared with length

between interrupt requests; otherwise the status cannot be recovered as non-maskable interrupt would simply

nested.

includes IMF) are automatically saved on the stack, but the accumulator and others are not. These registers are

saved by software if necessary. When multiple interrupt services are nested, it is also necessary to avoid using

the same data memory area for saving registers. The following methods are used to save/restore the general-

purpose registers.

a − 1

Example: Correspondence between vector table address for INTTBT and the entry address of the interrupt

A maskable interrupt is not accepted until the IMF is set to “1” even if the maskable interrupt higher than the

In order to utilize nested interrupt service, the IMF is set to “1” in the interrupt service program. In this case,

To avoid overloaded nesting, clear the individual interrupt enable flag whose interrupt is currently serviced,

During interrupt acceptance processing, the program counter (PC) and the program status word (PSW,

machine cycle on 10 cycle instruction) to start interrupt acceptance processing since its interrupt latch is set.

instruction

Execute

a

FFF2H

FFF3H

a + 1

Vector table address

n

Figure 3-2 Vector table address,Entry address

D2H

03H

Interrupt acceptance

a

n − 1

Vector

n − 2

Page 38

b

b + 1

b + 2

instruction

Execute

b + 3

n - 3

D203H

D204H

Entry address

c + 1

Interrupt service task

0FH

06H

n − 2 n − 1

c + 2

Execute RETI instruction

Interrupt

service

program

TMP86FH46ANG

a

a + 1

n

a + 2

Related parts for TMP86FH46ANG(Z)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: