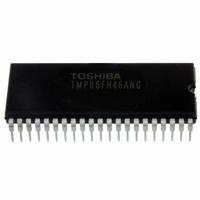

TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 38

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

- Current page: 38 of 214

- Download datasheet (3Mb)

2.2 System Clock Controller

(1)

(2)

Note: IDLE0 and SLEEP0 modes start/release without reference to TBTCR<TBTEN> setting.

TBTCR<TBTCK>. After the falling edge is detected, the program operation is resumed from the

instruction following the IDLE0 and SLEEP0 modes start instruction. Before starting the IDLE0 or

SLEEP0 mode, when the TBTCR<TBTEN> is set to “1”, INTTBT interrupt latch is set to “1”.

TBTCR<TBTCK> and INTTBT interrupt processing is started.

• Start the IDLE0 and SLEEP0 modes

• Release the IDLE0 and SLEEP0 modes

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the

Interrupt release mode (IMF•EF6•TBTCR<TBTEN> = “1”)

IDLE0 and SLEEP0 modes are released by the source clock falling edge, which is setting by the

Note 1: Because returning from IDLE0, SLEEP0 to NORMAL1, SLOW1 is executed by the asynchro-

Note 2: When a watchdog timer interrupt is generated immediately before IDLE0/SLEEP0 mode is

Normal release mode (IMF•EF6•TBTCR<TBTEN> = “0”)

of TBT and TBTCR<TBTEN>.

cleared to “0” and the operation mode is returned to the mode preceding IDLE0 and SLEEP0

modes. Before starting the IDLE0 or SLEEP0 mode, when the TBTCR<TBTEN> is set to “1”,

INTTBT interrupt latch is set to “1”.

After releasing reset, the operation mode is started from NORMAL1 mode.

Stop (Disable) peripherals such as a timer counter.

To start IDLE0 and SLEEP0 modes, set SYSCR2<TGHALT> to “1”.

IDLE0 and SLEEP0 modes include a normal release mode and an interrupt release mode.

These modes are selected by interrupt master flag (IMF), the individual interrupt enable flag

After releasing IDLE0 and SLEEP0 modes, the SYSCR2<TGHALT> is automatically

IDLE0 and SLEEP0 modes can also be released by inputting low level on the

nous internal clock, the period of IDLE0, SLEEP0 mode might be the shorter than the period set-

ting by TBTCR<TBTCK>.

started, the watchdog timer interrupt will be processed but IDLE0/SLEEP0 mode will not be

started.

Page 24

TMP86FH46ANG

RESET

pin.

Related parts for TMP86FH46ANG(Z)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: