TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 30

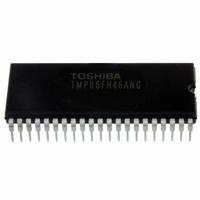

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

- Current page: 30 of 214

- Download datasheet (3Mb)

2.2 System Clock Controller

2.2.4 Operating Mode Control

2.2.4.1

Example 1 :Starting STOP mode from NORMAL mode by testing a port P20.

Note 8: Before setting TGHALT to “1”, be sure to stop peripherals. If peripherals are not stopped, the interrupt latch of peripherals

SSTOPH:

may be set after IDLE0 or SLEEP0 mode is released.

(STOP5 to STOP2) which is controlled by the STOP mode release control register (STOPCR).

The

started by setting SYSCR1<STOP> to “1”. During STOP mode, the following status is maintained.

selected with the SYSCR1<RELM>. Do not use any key-on wakeup input (STOP5 to STOP2) for releas-

ing STOP mode in edge-sensitive mode.

STOP mode

(1)

STOP mode is controlled by the system control register 1, the

STOP mode includes a level-sensitive mode and an edge-sensitive mode, either of which can be

Note 1: The STOP mode can be released by either the STOP or key-on wakeup pin (STOP5 to STOP2).

Note 2: During STOP period (from start of STOP mode to end of warm up), due to changes in the external

STOP

pin input which is enabled by STOPCR. This mode is used for capacitor backup when the main

power supply is cut off and long term battery backup.

to STOP2

ately. Thus, to start STOP mode in the level-sensitive release mode, it is necessary for the program to

first confirm that the

methods can be used for confirmation.

1. Oscillations are turned off, and all internal operations are halted.

2. The data memory, registers, the program status word and port output latches are all held in the

3. The prescaler and the divider of the timing generator are cleared to “0”.

4. The program counter holds the address 2 ahead of the instruction (e.g., [SET (SYSCR1).7])

Level-sensitive release mode (RELM = “1”)

In this mode, STOP mode is released by setting the

Even if an instruction for starting STOP mode is executed while

LD

TEST

JRS

DI

SET

status in effect before STOP mode was entered.

which started STOP mode.

However, because the STOP pin is different from the key-on wakeup and can not inhibit the release

input, the STOP pin must be used for releasing STOP mode.

interrupt pin signal, interrupt latches may be set to “1” and interrupts may be accepted immediately

after STOP mode is released. Before starting STOP mode, therefore, disable interrupts. Also, before

enabling interrupts after STOP mode is released, clear unnecessary interrupt latches.

pin is also used both as a port P20 and an

1. Testing a port.

2. Using an external interrupt input

input is low, STOP mode does not start but instead the warm-up sequence starts immedi-

(P2PRD). 0

(SYSCR1), 01010000B

F, SSTOPH

(SYSCR1). 7

STOP

pin input is low or STOP5 to STOP2 input is high. The following two

Page 16

; Sets up the level-sensitive release mode

; Wait until the

; IMF ← 0

; Starts STOP mode

INT5

(

INT5

INT5

STOP

pin input goes low level

(external interrupt input 5) pin. STOP mode is

STOP

is a falling edge-sensitive input).

STOP

pin high or setting the STOP5 to STOP2

pin input and key-on wakeup input

STOP

pin input is high or

TMP86FH46ANG

STOP5

Related parts for TMP86FH46ANG(Z)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: