R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 673

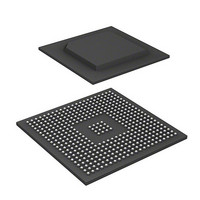

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 673 of 1694

- Download datasheet (9Mb)

13. PCI Controller (PCIC)

To access the address space in this LSI, use PCIMBAR0/1, PCILSR0/1, and PCILAR0/1. PCI

addresses can be allocated to by software. The PCIC has two types of registers for memory

mapping, Local Address Space 0 (base 0) and Local Address Space 1 (base 1).

By setting these two registers, two types of spaces (bases) can be allocated.

The size of these address spaces are selectable from 1 Mbyte to 512 Mbytes by PCILSR0/1.

Single-longword (32 bits) and burst transfers on the PCI bus are supported for PCI target memory

transfers.

For details of accesses to PCIC internal registers (PCI configuration registers and PCI local

registers), see after-mentioned description for configuration access and access to I/O space.

A certain range of the address space on the PCI bus corresponds to the local address space in the

internal bus address space. The local address space 0 in this LSI is controlled by PCIMBAR0,

PCILSR0 and PCILAR0. The local address space 1 is controlled by PCIMBAR1, PCILSR1 and

PCILAR1. Figure 13.11 shows the address translation from the PCI bus to the SuperHyway bus in

this LSI.

PCIMBAR indicates the start address of the PCI bus memory space used by an external PCI

device. PCILAR indicates the start address of the local address space for this LSI. PCILSR

indicates the size of the address space used by an external PCI device.

For PCIMBAR and PCILAR, the upper address bits that are higher than the memory size set in

PCILSR becomes valid. The upper bits in PCIMBAR and the PCI address output from an external

PCI device are compared to determine whether the PCIC is accessed. If these addresses match, an

access to the PCIC is recognized, and a local address is generated from the upper bits in PCILAR

and the lower bits of the PCI address output from the external PCI device. A PCI command

(memory read/write) is executed for this address. If the upper bits of the PCI address output from

the external PCI device does not match the upper bits of PCIMBAR, the PCIC does not respond to

a PCI command.

The PCIC supports data prefetching for a memory read command. When burst read is performed

on the PCI bus, data is prefetched in block units of 8 bytes or 32 bytes (set by PCICR.PFCS and

PCICR.PFE).

When all the MBARE bits in PCILSR0/1 are 0, a PCI bus address is transferred to the internal bus

without translation.

Rev.1.00 Jan. 10, 2008 Page 641 of 1658

REJ09B0261-0100

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: