ATMEGA324P-A15MZ Atmel, ATMEGA324P-A15MZ Datasheet - Page 253

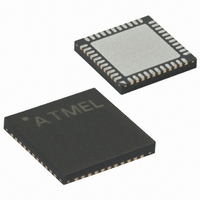

ATMEGA324P-A15MZ

Manufacturer Part Number

ATMEGA324P-A15MZ

Description

MCU AVR 32KB FLASH 15MHZ 44-VQFN

Manufacturer

Atmel

Series

AVR® ATmegar

Datasheet

1.ATMEGA324P-A15MZ.pdf

(346 pages)

Specifications of ATMEGA324P-A15MZ

Package / Case

44-VQFN Exposed Pad

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Operating Temperature

-40°C ~ 125°C

Speed

16MHz

Number Of I /o

32

Eeprom Size

1K x 8

Core Processor

AVR

Program Memory Type

FLASH

Ram Size

2K x 8

Program Memory Size

32KB (32K x 8)

Data Converters

A/D 8x10b

Oscillator Type

Internal

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Connectivity

I²C, SPI, UART/USART

Core Size

8-Bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 253 of 346

- Download datasheet (3Mb)

Programming Time for

Flash when using SPM

Simple Assembly

Code Example for a

Boot Loader

2503N–AVR–06/08

Flash corruption can easily be avoided by following these design recommendations (one is

sufficient):

1. If there is no need for a Boot Loader update in the system, program the Boot Loader Lock

2. Keep the AVR RESET active (low) during periods of insufficient power supply voltage.

3. Keep the AVR core in Power-down Sleep mode during periods of low V

The Calibrated RC Oscillator is used to time Flash accesses.

gramming time for Flash accesses from the CPU.

Table 98. SPM Programming Time.

Symbol

Flash write (Page Erase, Page

Write, and write Lock bits by SPM)

bits to prevent any Boot Loader software updates.

This can be done by enabling the internal Brown-out Detector (BOD) if the operating volt-

age matches the detection level. If not, an external low V

be used. If a reset occurs while a write operation is in progress, the write operation will be

completed provided that the power supply voltage is sufficient.

vent the CPU from attempting to decode and execute instructions, effectively protecting

the SPMCR Register and thus the Flash from unintentional writes.

.equ PAGESIZEB = PAGESIZE*2

.org SMALLBOOTSTART

Write_page:

Wrloop:

;-the routine writes one page of data from RAM to Flash

; the first data location in RAM is pointed to by the Y pointer

; the first data location in Flash is pointed to by the Z pointer

;-error handling is not included

;-the routine must be placed inside the boot space

; (at least the Do_spm sub routine). Only code inside NRWW section can

; be read during self-programming (page erase and page write).

;-registers used: r0, r1, temp1 (r16), temp2 (r17), looplo (r24),

; loophi (r25), spmcrval (r20)

; storing and restoring of registers is not included in the routine

; register usage can be optimized at the expense of code size

;-It is assumed that either the interrupt table is moved to the Boot

; loader section or that the interrupts are disabled.

; page erase

ldi

call Do_spm

; re-enable the RWW section

ldi

call Do_spm

; transfer data from RAM to Flash page buffer

ldi

ldi

ld

ld

ldi

call Do_spm

adiw ZH:ZL, 2

sbiw loophi:looplo, 2

brne Wrloop

spmcrval, (1<<PGERS) | (1<<SPMEN)

spmcrval, (1<<RWWSRE) | (1<<SPMEN)

looplo, low(PAGESIZEB)

loophi, high(PAGESIZEB)

r0, Y+

r1, Y+

spmcrval, (1<<SPMEN)

Min Programming Time

; PAGESIZEB is page size in BYTES, not

; words

;init loop variable

;not required for PAGESIZEB<=256

;use subi for PAGESIZEB<=256

3.7 ms

CC

Max Programming Time

Reset Protection circuit can

Table 98

ATmega32(L)

4.5 ms

shows the typical pro-

CC

. This will pre-

253

Related parts for ATMEGA324P-A15MZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 32K FLASH 44-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 32K FLASH 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 32K FLASH 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32K FLASH 20MHZ 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32KB FLASH 20MHZ 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32KB FLASH 20MHZ 44QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32KB FLASH 20MHZ 44TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32K FLASH 20MHZ 44-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 32K FLASH 15MHZ 44-TQFP

Manufacturer:

Atmel

Datasheet: