AT91SAM7X128-CU Atmel, AT91SAM7X128-CU Datasheet - Page 308

AT91SAM7X128-CU

Manufacturer Part Number

AT91SAM7X128-CU

Description

MCU ARM 128K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7X512-AU-999.pdf

(687 pages)

Specifications of AT91SAM7X128-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7X-EK - KIT EVAL FOR AT91SAM7X256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

AT91SAM7X128-CU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 308 of 687

- Download datasheet (11Mb)

30.6.1.1

30.6.1.2

Table 30-2.

308

Source Clock

3 686 400

4 915 200

5 000 000

7 372 800

MHz

AT91SAM7X512/256/128 Preliminary

Baud Rate in Asynchronous Mode

Baud Rate Calculation Example

Baud Rate Example (OVER = 0)

Expected Baud

If the external SCK clock is selected, the duration of the low and high levels of the signal pro-

vided on the SCK pin must be longer than a Master Clock (MCK) period. The frequency of the

signal provided on SCK must be at least 4.5 times lower than MCK.

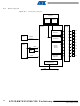

Figure 30-3. Baud Rate Generator

If the USART is programmed to operate in asynchronous mode, the selected clock is first

divided by CD, which is field programmed in the Baud Rate Generator Register (US_BRGR).

The resulting clock is provided to the receiver as a sampling clock and then divided by 16 or 8,

depending on the programming of the OVER bit in US_MR.

If OVER is set to 1, the receiver sampling is 8 times higher than the baud rate clock. If OVER is

cleared, the sampling is performed at 16 times the baud rate clock.

The following formula performs the calculation of the Baud Rate.

This gives a maximum baud rate of MCK divided by 8, assuming that MCK is the highest possi-

ble clock and that OVER is programmed at 1.

Table 30-2

clock frequencies. This table also shows the actual resulting baud rate and the error.

SCK

38 400

38 400

38 400

38 400

Rate

Bit/s

Reserved

MCK/DIV

Baudrate

MCK

shows calculations of CD to obtain a baud rate at 38400 bauds for different source

USCLKS

=

0

1

2

3

Calculation Result

--------------------------------------------

(

8 2 Over

SelectedClock

(

–

12.00

6.00

8.00

8.14

16-bit Counter

)CD

CD

)

USCLKS = 3

CD

12

6

8

8

0

SYNC

CD

>1

1

0

Actual Baud Rate

1

0

38 400.00

38 400.00

39 062.50

38 400.00

Bit/s

OVER

Sampling

Divider

FIDI

6120H–ATARM–17-Feb-09

0

1

SYNC

0.00%

0.00%

1.70%

0.00%

Error

SCK

Baud Rate

Sampling

Clock

Clock

Related parts for AT91SAM7X128-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: