M29W640GB60ZA6E NUMONYX, M29W640GB60ZA6E Datasheet - Page 41

M29W640GB60ZA6E

Manufacturer Part Number

M29W640GB60ZA6E

Description

Flash Mem Parallel 3V/3.3V 64M-Bit 8M x 8/4M x 16 60ns 48-Pin TFBGA Tray

Manufacturer

NUMONYX

Datasheet

1.M29W640GH70NB6E.pdf

(90 pages)

Specifications of M29W640GB60ZA6E

Package

48TFBGA

Cell Type

NOR

Density

64 Mb

Architecture

Sectored

Block Organization

Asymmetrical

Location Of Boot Block

Bottom

Typical Operating Supply Voltage

3|3.3 V

Sector Size

8KByte x 8|64KByte x 127

Timing Type

Asynchronous

Operating Temperature

-40 to 85 °C

Interface Type

Parallel

5.3

5.4

5.5

5.6

Error bit (DQ5)

The error bit can be used to identify errors detected by the program/erase controller. The

error bit is set to ’1’ when a program, block erase or chip erase operation fails to write the

correct data to the memory. If the error bit is set a Read/Reset command must be issued

before other commands are issued. The error bit is output on DQ5 when the status register

is read.

Note that the Program command cannot change a bit set to ’0’ back to ’1’ and attempting to

do so will set DQ5 to ‘1’. A bus read operation to that address will show the bit is still ‘0’. One

of the erase commands must be used to set all the bits in a block or in the whole memory

from ’0’ to ’1’.

Erase timer bit (DQ3)

The erase timer bit can be used to identify the start of program/erase controller operation

during a Block Erase command. Once the program/erase controller starts erasing the erase

timer bit is set to ’1’. Before the program/erase controller starts the erase timer bit is set to ’0’

and additional blocks to be erased may be written to the command interface. The erase

timer bit is output on DQ3 when the status register is read.

Alternative toggle bit (DQ2)

The alternative toggle bit can be used to monitor the program/erase controller during erase

operations. The alternative toggle bit is output on DQ2 when the status register is read.

During chip erase and block erase operations the toggle bit changes from ’0’ to ’1’ to ’0’,

etc., with successive bus read operations from addresses within the blocks being erased. A

protected block is treated the same as a block not being erased. Once the operation

completes the memory returns to read mode.

During erase suspend the alternative toggle bit changes from ’0’ to ’1’ to ’0’, etc. with

successive bus read operations from addresses within the blocks being erased. Bus read

operations to addresses within blocks not being erased will output the memory cell data as if

in read mode.

After an erase operation that causes the error bit to be set the alternative toggle bit can be

used to identify which block or blocks have caused the error. The alternative toggle bit

changes from ’0’ to ’1’ to ’0’, etc. with successive bus read operations from addresses within

blocks that have not erased correctly. The alternative toggle bit does not change if the

addressed block has erased correctly.

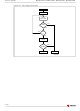

Figure 20: Toggle/alternative toggle bit polling AC waveforms (8-bit mode)

description of the data polling operation and timings.

Write to buffer and program abort bit (DQ1)

The write to buffer and program abort bit, DQ1, is set to ‘1’ when a write to buffer and

program operation aborts. Otherwise, DQ1 bit is set to ‘0’. The Write to Buffer and Program

Abort and Reset command must be issued to return the device to read mode (see Write to

Buffer and Program in the commands section).

gives a

41/90