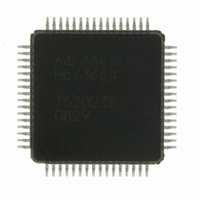

HD64F3664FPV Renesas Electronics America, HD64F3664FPV Datasheet - Page 225

HD64F3664FPV

Manufacturer Part Number

HD64F3664FPV

Description

IC H8/3664 MCU FLASH 32K 64LQFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300H Tinyr

Specifications of HD64F3664FPV

Core Size

16-Bit

Program Memory Size

32KB (32K x 8)

Oscillator Type

External

Core Processor

H8/300H

Speed

16MHz

Connectivity

I²C, SCI

Peripherals

PWM, WDT

Number Of I /o

29

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Operating Temperature

-20°C ~ 75°C

Package / Case

64-LQFP

No. Of I/o's

29

Ram Memory Size

2KB

Cpu Speed

16MHz

No. Of Timers

4

Digital Ic Case Style

LQFP

Supply Voltage

RoHS Compliant

Controller Family/series

H8/300H

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F3664FPV

Manufacturer:

MURATA

Quantity:

34 000

Company:

Part Number:

HD64F3664FPV

Manufacturer:

HD

Quantity:

465

Company:

Part Number:

HD64F3664FPV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

HD64F3664FPV

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 225 of 446

- Download datasheet (3Mb)

13.3

The watchdog timer is provided with an 8-bit counter. If 1 is written to WDON while writing 0 to

B2WI when the TCSRWE bit in TCSRWD is set to 1, TCWD begins counting up. (To operate

the watchdog timer, two write accesses to TCSRWD are required.) When a clock pulse is input

after the TCWD count value has reached H'FF, the watchdog timer overflows and an internal reset

signal is generated. The internal reset signal is output for a period of 256 φ

is a writable counter, and when a value is set in TCWD, the count-up starts from that value. An

overflow period in the range of 1 to 256 input clock cycles can therefore be set, according to the

TCWD set value.

Figure 13.2 shows an example of watchdog timer operation.

Example:

Operation

Internal reset

signal

count value

TCWD

With 30ms overflow period when

Therefore, 256 – 15 = 241 (H'F1) is set in TCW.

H'FF

H'00

4

8192

10

H'F1

Figure 13.2 Watchdog Timer Operation Example

6

H'F1 written

to TCWD

30

10

–3

Start

= 14.6

H'F1 written to TCWD

= 4 MHz

Rev. 6.00 Mar. 24, 2006 Page 195 of 412

256

Reset generated

osc

TCWD overflow

clock cycles

Section 13 Watchdog Timer

osc

clock cycles. TCWD

REJ09B0142-0600

Related parts for HD64F3664FPV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: