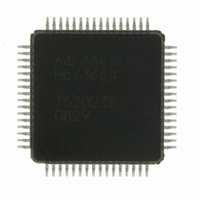

HD64F3664FPV Renesas Electronics America, HD64F3664FPV Datasheet - Page 260

HD64F3664FPV

Manufacturer Part Number

HD64F3664FPV

Description

IC H8/3664 MCU FLASH 32K 64LQFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300H Tinyr

Specifications of HD64F3664FPV

Core Size

16-Bit

Program Memory Size

32KB (32K x 8)

Oscillator Type

External

Core Processor

H8/300H

Speed

16MHz

Connectivity

I²C, SCI

Peripherals

PWM, WDT

Number Of I /o

29

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Operating Temperature

-20°C ~ 75°C

Package / Case

64-LQFP

No. Of I/o's

29

Ram Memory Size

2KB

Cpu Speed

16MHz

No. Of Timers

4

Digital Ic Case Style

LQFP

Supply Voltage

RoHS Compliant

Controller Family/series

H8/300H

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F3664FPV

Manufacturer:

MURATA

Quantity:

34 000

Company:

Part Number:

HD64F3664FPV

Manufacturer:

HD

Quantity:

465

Company:

Part Number:

HD64F3664FPV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

HD64F3664FPV

Manufacturer:

RENESAS/瑞萨

Quantity:

20 000

- Current page: 260 of 446

- Download datasheet (3Mb)

Section 14 Serial Communication Interface 3 (SCI3)

14.7

The SCI3 creates the following six interrupt requests: transmission end, transmit data empty,

receive data full, and receive errors (overrun error, framing error, and parity error). Table 14.6

shows the interrupt sources.

Table 14.6 SCI3 Interrupt Requests

The initial value of the TDRE flag in SSR is 1. Thus, when the TIE bit in SCR3 is set to 1 before

transferring the transmit data to TDR, a TXI interrupt request is generated even if the transmit data

is not ready. The initial value of the TEND flag in SSR is 1. Thus, when the TEIE bit in SCR3 is

set to 1 before transferring the transmit data to TDR, a TEI interrupt request is generated even if

the transmit data has not been sent. It is possible to make use of the most of these interrupt

requests efficiently by transferring the transmit data to TDR in the interrupt routine. To prevent

the generation of these interrupt requests (TXI and TEI), set the enable bits (TIE and TEIE) that

correspond to these interrupt requests to 1, after transferring the transmit data to TDR.

14.8

14.8.1

When framing error detection is performed, a break can be detected by reading the RxD pin value

directly. In a break, the input from the RxD pin becomes all 0, setting the FER flag, and possibly

the PER flag. Note that as the SCI3 continues the receive operation after receiving a break, even if

the FER flag is cleared to 0, it will be set to 1 again.

Rev. 6.00 Mar. 24, 2006 Page 230 of 412

REJ09B0142-0600

Interrupt Requests

Receive Data Full

Transmit Data Empty

Transmission End

Receive Error

Interrupts

Usage Notes

Break Detection and Processing

Abbreviation

RXI

TXI

TEI

ERI

Interrupt Sources

Setting RDRF in SSR

Setting TDRE in SSR

Setting TEND in SSR

Setting OER, FER, and PER in SSR

Related parts for HD64F3664FPV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: