MC68HC16Z1CFC16 Freescale Semiconductor, MC68HC16Z1CFC16 Datasheet - Page 114

MC68HC16Z1CFC16

Manufacturer Part Number

MC68HC16Z1CFC16

Description

IC MPU 1K RAM 16MHZ 132-PQFP

Manufacturer

Freescale Semiconductor

Series

HC16r

Specifications of MC68HC16Z1CFC16

Core Processor

CPU16

Core Size

16-Bit

Speed

16MHz

Connectivity

EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

132-QFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68HC16Z1CFC16

Manufacturer:

FREESCALE

Quantity:

1 410

Company:

Part Number:

MC68HC16Z1CFC16

Manufacturer:

FREESCALE

Quantity:

5 530

Company:

Part Number:

MC68HC16Z1CFC16

Manufacturer:

MOT

Quantity:

5 510

Company:

Part Number:

MC68HC16Z1CFC16

Manufacturer:

MOTOROLA

Quantity:

1

Part Number:

MC68HC16Z1CFC16

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

- Current page: 114 of 500

- Download datasheet (6Mb)

5-8

When a fast reference is used, three W bits are located in the PLL feedback path, en-

abling frequency multiplication by a factor from one to eight. Three Y bits and the X bit

are located in the VCO clock output path to provide the ability to slow the system clock

without disturbing the PLL.

When using a fast reference, the clock frequency is determined by SYNCR bit settings

as follows:

The reset state of SYNCR ($3F00) results in a power-on f

is 4.194 MHz.

For the device to perform correctly, both the clock frequency and VCO frequency (se-

lected by the W, X, and Y bits) must be within the limits specified for the MCU. In order

for the VCO frequency to be within specifications (less than or equal to the maximum

system clock frequency multiplied by two), the X bit must be set for system clock fre-

quencies greater than one-half the maximum specified system clock.

Internal VCO frequency is determined by the following equations:

On both slow and fast reference devices, when an external system clock signal is ap-

plied (MODCLK = 0 during reset), the PLL is disabled. The duty cycle of this signal is

critical, especially at operating frequencies close to maximum. The relationship be-

tween clock signal duty cycle and clock signal period is expressed as follows:

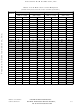

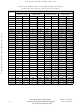

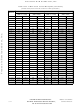

Tables

SYNCR bits. To obtain clock frequency, find the counter modulus in the leftmost col-

umn, then multiply the reference frequency by the value in the appropriate prescaler

cell. Shaded areas indicate which values exceed the specifications for a device rated

at a particular operating frequency. Refer to

TERISTICS

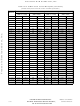

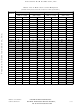

Tables

SYNCR bits. To obtain clock frequency, find the counter modulus in the leftmost col-

umn, then refer to appropriate prescaler cell. Shaded areas indicate which values ex-

ceed the specifications for a device rated at a particular operating frequency. Refer to

APPENDIX A ELECTRICAL CHARACTERISTICS

(f

).

5-2, 5-3, and

5-5, 5-6, and

Minimum External Clock Period

------------------------------------------------------------------------------------------------------------------------------- ---------------------------------------- -

50% Percentage Variation of External Clock Input Duty Cycle

for maximum allowable clock rate.

–

Freescale Semiconductor, Inc.

5-4

5-7

For More Information On This Product,

Minimum External Clock High/Low Time

show clock control multipliers for all possible combinations of

show actual clock frequencies for the same combinations of

SYSTEM INTEGRATION MODULE

f

sys

Go to: www.freescale.com

=

f

f

VCO

VCO

--------- - 4 Y

128

f

ref

=

=

2f

4f

or

sys

sys

+

APPENDIX A ELECTRICAL CHARAC-

=

1

if X = 0

if X = 1

2

2W

for maximum system frequency

+

X

sys

of 8.388 MHz when f

M68HC16 Z SERIES

USER’S MANUAL

ref

Related parts for MC68HC16Z1CFC16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: