COP8SA-DM National Semiconductor, COP8SA-DM Datasheet - Page 46

COP8SA-DM

Manufacturer Part Number

COP8SA-DM

Description

MODULE DEBUGGING FOR COP8SA

Manufacturer

National Semiconductor

Datasheet

1.DM-COP820D.pdf

(254 pages)

Specifications of COP8SA-DM

Module/board Type

Debugger Module

For Use With/related Products

Cop 8

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*COP8SA-DM

- Current page: 46 of 254

- Download datasheet (2Mb)

COPSAx7 I/O structure minimizes external component requirements. Software-

switchable I/O enables designers to reconfigure the microcontroller's I/O functions with

a single instruction. Each individual I/O pin can be independently configured as an

output pin low, an output high, an input with high impedance or an input with a weak

pull-up device. A typical example is the use of I/O pins as the keyboard matrix input lines.

The input lines can be programmed with internal weak pull-ups so that the input lines

read logic high when the keys are all up. With a key closure, the corresponding input line

will read a logic zero since the weak pull-up can easily be overdriven. When the key is

released, the internal weak pull-up will pull the input line back to logic high. This

flexibility eliminates the need for external pull-up resistors. The High current options are

available for driving LEDs, motors and speakers. This flexibility helps to ensure a

cleaner design, with less external components and lower costs. Below is the general

description of all available pins.

V

CKI is the clock input. This can come from the Internal R/C oscillator, external, or a

crystal oscillator (in conjunction with CKO). See Oscillator Description section.

RESET is the master reset input. See Reset description section.

The device contains four bidirectional 8-bit I/O ports (C, G, L and F), where each

individual bit may be independently configured as an input (Schmitt trigger inputs on

ports L and G), output or TRI-STATE under program control. Three data memory

address locations are allocated for each of these I/O ports. Each I/O port has two

associated 8-bit memory mapped registers, the CONFIGURATION register and the

output DATA register. A memory mapped address is also reserved for the input pins of

each I/O port. (See the memory map for the various addresses associated with the I/O

ports.) Figure 2-4 shows the I/O port configurations. The DATA and CONFIGURATION

registers allow for each port bit to be individually configured under software control as

shown below:

Port L is an 8-bit I/O port. All L-pins have Schmitt triggers on the inputs.

Port L supports the Multi-Input Wake Up feature on all eight pins. The 16-pin device

does not have a full complement of Port L pins. The unavailable pins are not terminated.

A read operation these unterminated pins will return unpredictable values. To minimize

current drain, the unavailable pins must be programmed as outputs.

2-8

CC

and GND are the power supply pins. All V

COP8SAx7 MICROCONTROLLER

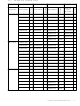

CONFIGURATION

Register

0

0

1

1

Register

DATA

0

1

0

1

CC

Hi-Z Input

(TRI-STATE Output)

Input with Weak Pull-Up

Push-Pull Zero Output

Push-Pull One Output

and GND pins must be connected.

Port Set-Up

Related parts for COP8SA-DM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

PROGRAMING UNIT FOR COP8SA PARTS

Manufacturer:

National Semiconductor

Part Number:

Description:

ADAPTER SOIC 16,20,28,44 PLCC

Manufacturer:

National Semiconductor

Part Number:

Description:

8-Bit CMOS ROM Based and One-Time Programmable OTP Microcontroller with 1k to 4k Memory/ Power On Reset/ and Very Small Packaging

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

National Semiconductor [8-Bit D/A Converter]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

National Semiconductor [Media Coprocessor]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

AC97 Rev 2 Codec with Sample Rate Conversion and National 3D Sound

Manufacturer:

National Semiconductor

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

General Purpose, Low Voltage, Low Power, Rail-to-Rail Output Operational Amplifiers

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

8-bit 20 MSPS flash A/D converter.

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Low Noise Quad Operational Amplifier

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Quad Differential Line Receivers

Manufacturer:

National Semiconductor

Datasheet: