COP8SA-DM National Semiconductor, COP8SA-DM Datasheet - Page 50

COP8SA-DM

Manufacturer Part Number

COP8SA-DM

Description

MODULE DEBUGGING FOR COP8SA

Manufacturer

National Semiconductor

Datasheet

1.DM-COP820D.pdf

(254 pages)

Specifications of COP8SA-DM

Module/board Type

Debugger Module

For Use With/related Products

Cop 8

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*COP8SA-DM

- Current page: 50 of 254

- Download datasheet (2Mb)

the Program Counter (PC).

2.8.2

The program memory consists of 1024, 2048, or 4096 bytes of EPROM. Table 2-1 shows

the program memory sizes for the different devices. These bytes may hold program

instructions or constant data (data tables for the LAID instruction, jump vectors for the

JID instruction, and interrupt vectors for the VIS instruction). The program memory is

addressed by the 15-bit program counter (PC). All interrupts in the device vector to

program memory location 0FF Hex. The contents of the program memory read 00 Hex in

the erased state.

2.8.3

The data memory address space includes the on-chip RAM and data registers, the I/O

registers (Configuration, Data and Pin), the control registers, the MICROWIRE/PLUS

SIO shift register, and the various registers, and counters associated with the timers

(with the exception of the IDLE timer). Data memory is addressed directly by the

instruction or indirectly by the B, X and SP pointers.

The data memory consists of 64 or 128 bytes of RAM. Table 2-1 shows the data memory

sizes for the different devices. Fifteen bytes of RAM are mapped as “registers” at

addresses 0F0 to 0FE Hex. These registers can be loaded immediately, and also

decremented and tested with the DRSZ (decrement register and skip if zero) instruction.

The memory pointer registers X, SP and B are memory mapped into this space at address

locations 0FC to 0FE Hex respectively, with the other registers (except 0FF) being

available for general usage. Address location 0FF is reserved for future RAM expansion.

If compatibility with future devices (with more RAM) is not desired, this location can be

used as a general purpose RAM location.

The instruction set permits any bit in memory to be set, reset or tested. All I/O and

registers (except A and PC) are memory mapped; therefore, I/O bits and register bits can

be directly and individually set, reset and tested. The accumulator (A) bits can also be

directly and individually tested.

RAM contents are undefined upon power-up.

2-12

COP8SAx7 MICROCONTROLLER

Program Memory

Data Memory

COP8SAA7

COP8SAB7

COP8SAC7

Device

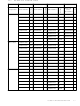

Table 2-1 Program/Data Memory Sizes

Program

Memory

(Bytes)

1024

2048

4096

64

128

128

Data Memory

(Bytes)

User Storage

8

8

8

(Bytes)

Related parts for COP8SA-DM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

PROGRAMING UNIT FOR COP8SA PARTS

Manufacturer:

National Semiconductor

Part Number:

Description:

ADAPTER SOIC 16,20,28,44 PLCC

Manufacturer:

National Semiconductor

Part Number:

Description:

8-Bit CMOS ROM Based and One-Time Programmable OTP Microcontroller with 1k to 4k Memory/ Power On Reset/ and Very Small Packaging

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

National Semiconductor [8-Bit D/A Converter]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

National Semiconductor [Media Coprocessor]

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Digitally Controlled Tone and Volume Circuit with Stereo Audio Power Amplifier, Microphone Preamp Stage and National 3D Sound

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

AC97 Rev 2 Codec with Sample Rate Conversion and National 3D Sound

Manufacturer:

National Semiconductor

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

General Purpose, Low Voltage, Low Power, Rail-to-Rail Output Operational Amplifiers

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

8-bit 20 MSPS flash A/D converter.

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Low Noise Quad Operational Amplifier

Manufacturer:

National Semiconductor

Datasheet:

Part Number:

Description:

Quad Differential Line Receivers

Manufacturer:

National Semiconductor

Datasheet: