NS32FX164AV-25 National Semiconductor, NS32FX164AV-25 Datasheet - Page 93

NS32FX164AV-25

Manufacturer Part Number

NS32FX164AV-25

Description

IC IMAGING COMM SGNL PROC PLCC68

Manufacturer

National Semiconductor

Datasheet

1.NS32FX164AV-25.pdf

(102 pages)

Specifications of NS32FX164AV-25

Processor Type

Advanced Imaging/Communications Signal Processor SIAP™

Speed

50MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

68-PLCC

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Other names

*NS32FX164AV-25

Q1284286

Q1284286

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

NS32FX164AV-25

Manufacturer:

NSC

Quantity:

12 388

Company:

Part Number:

NS32FX164AV-25

Manufacturer:

Texas Instruments

Quantity:

10 000

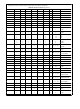

Appendix B Instruction Execution Times

B 1 2 Notes on Table Use

Values in the

effective addresses need to be calculated

A value of 1 indicates that address calculation time is re-

quired for the corresponding operand A 0 indicates that the

operand is either missing or it is in a register and the in-

struction has an optimized form which eliminates the TEA

calculation for it

In the L column multiply the entry by the operation length in

bytes (1 2 or 4)

In the TCY column special notations sometimes appear

n1

n1%n2 means that the instruction flushes the instruction

queue after n1 clock cycles and nonsequentially fetches the

next instruction The value n2 indicates the number of clock

cycles for the internal execution of the instruction (including

n1)

The effective number of cycles (TCY) must take into ac-

count the time (T

next instruction including the basic encoding and the index

bytes This time depends on the size and the alignment of

this portion

If only one memory cycle is required then

If more than one memory cycle is required then

In the notes column notations held within angle brackets

k l

which affect the execution time A table entry which is af-

fected by the operand addressing may have multiple values

corresponding to the alternatives These addressing nota-

tions are

k

k

k

k

k

k

Note Unless otherwise specified the TCY value for immediate addressing is

TOPi

I

R

M

F

x

ab

l

l

l

l

l

Tf

l

Ti

the same as for CPU register addressing

L

indicate alternatives in the operand addressing modes

f

Immediate

CPU Register

Memory

FPU Register either 32 or 64 Bits

Any Addressing Mode

a and b represent the addressing modes of operand

1 and 2 respectively Both a and b can be any ad-

dressing mode (e g

register)

n2 means n1 minimum n2 maximum

If operand is in a register or is immediate then

TOPi

else if i

else if i

else (i

If i (operation length)

else if i

else (i

If standard floating (32 bits) f

If long floating (64 bits) f

Tf

If integer

If integer

e

e

4

TEA1 and

e

e

e

e

e

TCY

TCY

fetch

0

e

e

double-word) then TOPi

double-word) L

byte then TOPi

word then TOPi

word then L

byte or word then Ti

double-word then Ti

) required to fetch the portion of the

e

e

n1

n1

TEA2 columns indicate whether

k

a

a

MR

e

6

5

e

a

a

l

byte then L

e

e

T

T

2

means memory to CPU

e

e

fetch

fetch

4

2

TOPB

TOPW

e

1

e

e

e

e

4

2

TOPD

1

93

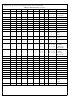

B 1 3 Calculation of the Execution Time TEX for

Basic Instructions

The execution time for a basic instruction is obtained by

performing the following steps

1 Find the desired instruction in Table B-1

2 Calculate the values of TEA TOPB etc using the num-

3 The result derived by adding together these values is the

EXAMPLE

Calculate TEX for the instruction CMPW R0 TOS

Operand 1 is in a register Operand 2 is in memory This

means that we must use the table values corresponding to

the

Only the

values assigned for the CMPi instruction Therefore they

are they only ones that need to be calculated to find TEX

The blank columns are irrelevant to this instruction

Both

case This means that effective address times have to be

calculated for both operands (For the

Register operand would have required no TEA time there-

fore only the Memory operand TEA would have been neces-

sary ) From the equations

TEA1 (Register mode)

TEA2 (Top of Stack mode access class read)

The

to or from memory For a Compare instruction each oper-

and is read once for a total of two operand transfers

TCY is the time required for internal operation within the

CPU The TCY value for this case is 3

TEX

If the CPU is running at 20 MHz then a machine cycle (clock

cycle) is 50 ns Therefore this instruction would take 10

50 ns or 0 5 s to execute

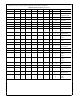

B 1 4 Calculation of the Execution Time TEX for

Floating-Point Instructions

The execution time for a floating-point instruction is ob-

tained by performing the following steps

1 Find the desired instruction in Table B-2

2 Calculate the values of TEA1 TEA2 TOPB etc using

3 Get the floating-point instruction execution time TFPU

4 Choose the higher value between TPR and TFPU

5 The result derived by adding together these values is the

EXAMPLE 1

Calculate TEX for the instruction MOVLF F0

Assumptions

e

TOPi (Word Register)

TOPi (Word TOS)

Total TOPi

The FPU being used is the NS32181

Write cycles are performed with no wait states

(Continued)

bers in the table and the equations given in the previous

sections

execution time TEX in clock cycles

the numbers in the table and the equations given in the

previous sections

from the appropriate FPU data sheet

execution time TEX in clock cycles

10 machine cycles

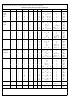

k

e

xM

TOPi column represents potential operand transfers

TEA1 and

TEA1

l

TEA1

case as given in the Notes column

e

a

3

TEA2

TEA2 columns contain 1 for the

TEA2

e

e

a

3 (assuming the operand aligned)

e

2

TOPi

0

TOPi and TCY columns have

a

TCY

e

k

MR

2

a

l

h 3000

e

2

case the

a

2

k

3

a

xM

a

3

l

c

3