NS32FX164AV-25 National Semiconductor, NS32FX164AV-25 Datasheet - Page 94

NS32FX164AV-25

Manufacturer Part Number

NS32FX164AV-25

Description

IC IMAGING COMM SGNL PROC PLCC68

Manufacturer

National Semiconductor

Datasheet

1.NS32FX164AV-25.pdf

(102 pages)

Specifications of NS32FX164AV-25

Processor Type

Advanced Imaging/Communications Signal Processor SIAP™

Speed

50MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

68-PLCC

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Other names

*NS32FX164AV-25

Q1284286

Q1284286

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

NS32FX164AV-25

Manufacturer:

NSC

Quantity:

12 388

Company:

Part Number:

NS32FX164AV-25

Manufacturer:

Texas Instruments

Quantity:

10 000

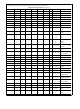

Mnemonic

ABSi

ACBi

ADDi

ADDCi

ADDPi

ADDQi

ADDR

ADJSPi

ANDi

ASHi

Bcond

BICi

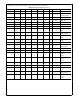

Appendix B Instruction Execution Times

TEX Calculation

Operand 1 is in a register operand 2 is in memory This

means that we have to use the table values for the

case

The following parameter values are obtained from Table B-2

and the equations in the previous sections

TEA2 (Absolute Mode)

TOPD (Memory Write)

Tf

TCY

TPR

From the FPU Execution Timing table in the NS32181 data

sheet we get a TFPU for MOVLF of 19 clock cycles

The higher value between TPR and TFPU

total execution time in clock cycles is

EXAMPLE 2

Calculate TEX for the instruction MULF 20(R0) 4(10(FP))

Assumptions

The FPU being used is the NS32181

20(R0) is an aligned read with one wait state

10(FP) is an aligned read with no wait states

4(10 (FP)) is an unaligned rmw with two wait states

e

e

e

TEX

4

32

TEA2

e

TEA2

a

TEA1

6

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

a

e

TOPD

4

e

e

a

7 (Operand aligned no waits)

4

6

TEA2

a

e

1

1

1

1

1

1

1

1

1

1

1

TF

10

a

TCY

TOPB

1

a

a

22

3 is 22 The

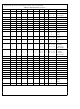

TABLE B-1 Basic Instructions

e

65

k

TOPW

FM

l

94

TOPD

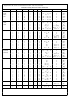

TEX Calculation

Operand 1 and operand 2 are both in memory Therefore

the table values for the

The parameter values obtained from Table B-2 and the

equations in the previous sections are as follows

TEA1

TEA2

TOPD

TOPD

T

TCY

TPR

From the FPU Execution Timing Table in the NS32181 data

sheet we get a TFPU for MULF of 33 clock cycles

The higher value between TPR and TFPU

total execution time in clock cycles is

1

f

(Continued)

TEX

36

e

e

e

e

4

1

2

5

e

22

0

(Register Relative Mode)

(Memory Relative Mode)

(TOPD

(Read from GEN1)

Aligned One Wait)

(RMW from GEN2)

ligned Two Waits)

a

TEA1

15

TOPi

2

2

2

2

3

1

3

1

3

3

2

1

3

1

2

3

1

a

9

e

a

28

a

TEA2

7 (Operand Aligned No Wait))

17

a

L

a

(22

k

TOPD

MM

e

14

l

e

15%20

17%22

11

6%10

28)

TCY

1

case must be used

18

16

16

18

a

9

8

3

4

4

3

4

4

6

4

2

3

6

3

4

4

7

3

4

4

a

7

e

a

TOPD

e

6

45

a

36

5

e

8

e

2

17 (Operand Una-

2

133

a

a

e

SCR

SCR

k

k

k

k

k

k

k

k

k

k

No Carry

Carry

k

k

k

k

k

k

k

no branch

branch

k

k

k

a

3 T

TOPD

M

M

R

R

xM

MR

RR

xM

MR

RR

M

R

xM

xR

xM

MR

RR

xM

MR

RR

3 is 36 The

9 (Operand

l

l

l

l

l

l

l

f

Notes

l

l

l

l

l

k

l

l

l

l

l

l

l

l

l

a

140

no branch

branch

no branch

branch

0

0

TCY

e

a

15