LPC1767FBD100,551 NXP Semiconductors, LPC1767FBD100,551 Datasheet - Page 525

LPC1767FBD100,551

Manufacturer Part Number

LPC1767FBD100,551

Description

IC ARM CORTEX MCU 512K 100-LQFP

Manufacturer

NXP Semiconductors

Series

LPC17xxr

Datasheets

1.LPC1767FBD100551.pdf

(2 pages)

2.LPC1767FBD100551.pdf

(840 pages)

3.LPC1767FBD100551.pdf

(65 pages)

Specifications of LPC1767FBD100,551

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

100MHz

Connectivity

Ethernet, I²C, IrDA, Microwire, SPI, SSI, UART/USART

Peripherals

Brown-out Detect/Reset, DMA, I²S, Motor Control PWM, POR, PWM, WDT

Number Of I /o

70

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 3.6 V

Data Converters

A/D 8x12b, D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Processor Series

LPC17

Core

ARM Cortex M3

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2, MCB1760, MCB1760U, MCB1760UME

For Use With

622-1005 - USB IN-CIRCUIT PROG ARM7 LPC2K

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

568-4967

935289808551

935289808551

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LPC1767FBD100,551

Manufacturer:

NXP Semiconductors

Quantity:

10 000

- Current page: 525 of 840

- Download datasheet (6Mb)

NXP Semiconductors

25.7 Register description

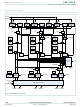

Table 454. Motor Control Pulse Width Modulator (MCPWM) register map

UM10360

User manual

Name

MCCON

MCCON_SET

MCCON_CLR

MCCAPCON

MCCAPCON_SET

MCCAPCON_CLR

MCTC0

MCTC1

MCTC2

MCLIM0

MCLIM1

MCLIM2

MCMAT0

MCMAT1

MCMAT2

MCDT

MCCP

MCCAP0

MCCAP1

MCCAP2

MCINTEN

MCINTEN_SET

MCINTEN_CLR

MCCNTCON

MCCNTCON_SET

MCCNTCON_CLR

MCINTF

MCINTF_SET

MCINTF_CLR

MCCAP_CLR

Description

PWM Control read address

PWM Control set address

PWM Control clear address

Capture Control read address

Capture Control set address

Event Control clear address

Timer Counter register, channel 0

Timer Counter register, channel 1

Timer Counter register, channel 2

Limit register, channel 0

Limit register, channel 1

Limit register, channel 2

Match register, channel 0

Match register, channel 1

Match register, channel 2

Dead time register

Commutation Pattern register

Capture register, channel 0

Capture register, channel 1

Capture register, channel 2

Interrupt Enable read address

Interrupt Enable set address

Interrupt Enable clear address

Count Control read address

Count Control set address

Count Control clear address

Interrupt flags read address

Interrupt flags set address

Interrupt flags clear address

Capture clear address

“Control” registers and “interrupt” registers have separate read, set, and clear addresses.

Reading such a register’s read address(e.g. MCCON) yields the state of the register bits.

Writing ones to the set address (e.g. MCCON_SET) sets register bit(s), and writing ones

to the clear address (e.g. MCCON_CLR) clears register bit(s).

The Capture registers (MCCAP) are read-only, and the write-only MCCAP_CLR address

can be used to clear one or more of them. All the other MCPWM registers (MCTIM,

MCPER, MCPW, MCDEADTIME, and MCCP) are normal read-write registers.

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 19 August 2010

Access

RO

WO

WO

RO

WO

WO

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RO

RO

RO

RO

WO

WO

RO

WO

WO

RO

WO

WO

WO

Chapter 25: LPC17xx Motor control PWM

Reset value

0

-

-

0

-

-

0

0

0

0xFFFF FFFF 0x400B 8024

0xFFFF FFFF 0x400B 8028

0xFFFF FFFF 0x400B 802C

0xFFFF FFFF 0x400B 8030

0xFFFF FFFF 0x400B 8034

0xFFFF FFFF 0x400B 8038

0x3FFF FFFF 0x400B 803C

0

0

0

0

0

-

-

0

-

-

0

-

-

-

UM10360

© NXP B.V. 2010. All rights reserved.

0x400B 8000

0x400B 8004

0x400B 8008

0x400B 800C

0x400B 8010

0x400B 8014

0x400B 8018

0x400B 801C

0x400B 8020

0x400B 8040

0x400B 8044

0x400B 8048

0x400B 804C

0x400B 8050

0x400B 8054

0x400B 8058

0x400B 8060

0x400B 8064

0x400B 8068

0x400B 806C

0x400B 8070

0x400B 8074

Address

0x400B 805C

525 of 840

Related parts for LPC1767FBD100,551

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

32-bit ARM Cortex-M3 microcontroller; up to 512 kB flash and 64 kB SRAM with Ethernet, USB 2.0 Host/Device/OTG, CAN

Manufacturer:

NXP [NXP Semiconductors]

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2420/2460 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2458 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2468 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2470 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2478 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The XA-S3 device is a member of Philips Semiconductors? XA(eXtended Architecture) family of high performance 16-bitsingle-chip microcontrollers

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP BlueStreak LH75401/LH75411 family consists of two low-cost 16/32-bit System-on-Chip (SoC) devices

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3130/3131 combine an 180 MHz ARM926EJ-S CPU core, high-speed USB2

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3141 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3143 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3152 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3154 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors