DF2552BR26DV Renesas Electronics America, DF2552BR26DV Datasheet - Page 220

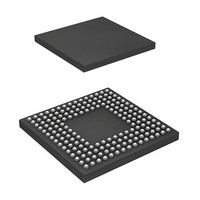

DF2552BR26DV

Manufacturer Part Number

DF2552BR26DV

Description

IC H8S/2552 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2552BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2552BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 220 of 980

- Download datasheet (6Mb)

Section 8 Data Transfer Controller (DTC)

8.2.3

SAR is a 24-bit register that designates the source address of data to be transferred by the DTC.

For word-size transfer, specify an even source address.

8.2.4

DAR is a 24-bit register that designates the destination address of data to be transferred by the

DTC. For word-size transfer, specify an even destination address.

8.2.5

CRA is a 16-bit register that designates the number of times that data is transferred by the DTC.

In normal mode, the entire CRA functions as a 16-bit transfer counter (1 to 65536). It is

decremented by 1 every time data is transferred, and transfer ends when the count reaches H'0000.

In repeat mode or block transfer mode, the CRA is divided into two parts; the upper 8 bits

(CRAH) and the lower 8 bits (CRAL). In repeat mode, CRAH holds the number of transfers while

CRAL functions as an 8-bit transfer counter (1 to 256). In block transfer mode, CRAH holds the

block size while CRAL functions as an 8-bit block size counter (1 to 256). CRAL is decremented

by 1 every time data is transferred, and the contents of CRAH are sent when the count reaches

H'00. These operations are repeated.

8.2.6

CRB is a 16-bit register that designates the number of times that data is transferred by the DTC in

block transfer mode. It functions as a 16-bit transfer counter (1 to 65536) that is decremented by 1

every time data is transferred, and transfer ends when the count reaches H'0000.

8.2.7

DTCER is a set of registers to specify the DTC activation interrupt source, and comprised of eight

registers; DTCERA to DTCERG, and DTCERI. The correspondence between interrupt sources

and DTCE bits, and vector numbers generated by the interrupt controller are shown in table 8.2.

For DTCE bit setting, use bit manipulation instructions such as BSET and BCLR for reading and

writing. When multiple activation sources are to be set at one time, only at the initial setting,

writing data is enabled after executing a dummy read on the relevant register with all the interrupts

being masked.

Rev. 6.00 Sep. 24, 2009 Page 172 of 928

REJ09B0099-0600

DTC Source Address Register (SAR)

DTC Destination Address Register (DAR)

DTC Transfer Count Register A (CRA)

DTC Transfer Count Register B (CRB)

DTC Enable Registers A to G, and I (DTCERA to DTCERG, and DTCERI)

Related parts for DF2552BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: