DF2552BR26DV Renesas Electronics America, DF2552BR26DV Datasheet - Page 598

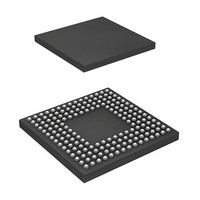

DF2552BR26DV

Manufacturer Part Number

DF2552BR26DV

Description

IC H8S/2552 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2552BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2552BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 598 of 980

- Download datasheet (6Mb)

Section 17 IEBus™ Controller (IEB) [H8S/2552 Group]

(b) Acknowledge bit at the End of the Control Field

Note: See section 17.1.3 (1), Slave Status Read (Control Bits: H'0, H'6).

(c) Acknowledge Bit at the End of the Message Length Field

(d) Acknowledge Bit at the End of the Data Field

Note: In this case, data field is transferred repeatedly until the number of data reaches the

Rev. 6.00 Sep. 24, 2009 Page 550 of 928

REJ09B0099-0600

The acknowledge bit at the end of the control field becomes NAK in the following cases and

transfer is stopped.

⎯ When the parity of the control bits is incorrect

⎯ When bit 3 in the control bits is 1 (data write) although the slave receive buffer* is not

⎯ When the control bits are set to the data read (H'3, H'7) although the slave transmit buffer*

⎯ When another unit which locked the slave unit requests H'3, H'6, H'7, H'A, H'B, H'E, or

⎯ When the control bits are the locked address read (H'4, H'5) although the unit is not locked

⎯ When a timing error occurs

⎯ When the control bits are undefined

The acknowledge bit at the end of the message length field becomes NAK in the following

cases and transfer is stopped.

⎯ When the parity of the message length bits is incorrect

⎯ When a timing error occurs

The acknowledge bit at the end of the data field becomes NAK in the following cases and

transfer is stopped.

⎯ When the parity of the data bits is incorrect*

⎯ When a timing error occurs after the previous transfer of the acknowledge bit

⎯ When the receive buffer becomes full and cannot accept further data

empty

is empty

H'F in the control bits although the slave unit has been locked

maximum number of transfer bytes if the number of data does not exceed the maximum

number of transfer bytes in one frame.

Related parts for DF2552BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: