PM4328-PI PMC-Sierra, Inc., PM4328-PI Datasheet - Page 189

PM4328-PI

Manufacturer Part Number

PM4328-PI

Description

Framer, T1|E1|T3 Standard Format, 324-BGA

Manufacturer

PMC-Sierra, Inc.

Datasheet

1.PM4328-PI.pdf

(250 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PM4328-PI

Manufacturer:

ATMEL

Quantity:

320

- Current page: 189 of 250

- Download datasheet (2Mb)

STANDARD PRODUCT

DATASHEET

PMC-2011596

12.14.1

PROPRIETARY AND CONFIDENTIAL

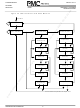

The boundary scan architecture consists of a TAP controller, an instruction

register with instruction decode, a bypass register, a device identification register

and a boundary scan register. The TAP controller interprets the TMS input and

generates control signals to load the instruction and data registers. The

instruction register with instruction decode block is used to select the test to be

executed and/or the register to be accessed. The bypass register offers a single-

bit delay from primary input, TDI to primary output, TDO. The device

identification register contains the device identification code.

The boundary scan register allows testing of board inter-connectivity. The

boundary scan register consists of a shift register placed in series with device

inputs and outputs. Using the boundary scan register, all digital inputs can be

sampled and shifted out on primary output, TDO. In addition, patterns can be

shifted in on primary input, TDI, and forced onto all digital outputs.

The TAP controller is a synchronous finite state machine clocked by the rising

edge of primary input, TCK. All state transitions are controlled using primary

input, TMS. The finite state machine is described below.

TAP Controller

ISSUE 1

176

HIGH DENSITY T1/E1 FRAMER

AND M13 MULTIPLEXER

PM4328 TECT3

Related parts for PM4328-PI

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

High density T1/E1 framer with intefrated M13 multiplexer

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

2 Megabit (256K x 8) 5.0 Volt-only CMOS Flash Memory

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

Interface, Multi-rate Telecom Backplane SERDES for 2.5Gbit/s Interconnect

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

processor, Spectra-9953 Device Driver

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

Ethernet, 8 Channel 10/100 Ethernet over SONET/SDH Mapping Device

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

Interface, Single Chip ADM for 622 & 155Mbit/s

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

Interface, Single Chip ADM for 622 & 155Mbit/s

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

Interface, Multi-rate SATURN User Network Interface for 2x622 and 4x155

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

SONET/SDH TRIBUTARY UNIT PAYLOAD PROCESSOR

Manufacturer:

PMC-Sierra, Inc.

Datasheet:

Part Number:

Description:

Processor, SONET/SDH Tributary Unit Payload Processor for 2488.32Mbit/s

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER AND M13 MULTIPLEXER

Manufacturer:

PMC-Sierra, Inc.

Datasheet:

Part Number:

Description:

SONET/SDH, Single Chip 96 Port SONET/SDH Cross-Connect Switch Element

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

ATM, Sixteen Channel ATM PHY Interface for 155.52 Mbps

Manufacturer:

PMC-Sierra, Inc.

Part Number:

Description:

ATM UNI, Single Channel ATM PHY Interface for 2488.32Mbps

Manufacturer:

PMC-Sierra, Inc.

Datasheet:

Part Number:

Description:

Interface, 4-Channel ATM and Bit HDLC User Network Interface

Manufacturer:

PMC-Sierra, Inc.