cx28394 Conexant Systems, Inc., cx28394 Datasheet - Page 114

cx28394

Manufacturer Part Number

cx28394

Description

Quad/x16/octal-t1/e1/j1 Framers

Manufacturer

Conexant Systems, Inc.

Datasheet

1.CX28394.pdf

(305 pages)

- Current page: 114 of 305

- Download datasheet (3Mb)

2.0 Circuit Description

2.5 Microprocessor Interface

2.5.1 Address/Data Bus

2.5.2 Bus Control Signals

2.5.3 Interrupt Requests

2-56

In Non-Multiplexed Address Mode, A[11:0] (A[10:0] for CX28394) provides the

address for the register access. In Multiplexed Address Mode, A[11:8] (A[10:8]

for CX28394) and AD[7:0] provide the address. In both modes, the data bytes

flow over the shared bidirectional, byte-wide bus, AD[7:0].

Four signals control operation of the interface port. The control signals are

AS*/ALE, CS*, DS*/RD*, and R/W*(WR*). An additional pin, MOTO*, selects

whether the interface signals are of a Motorola or Intel style.

and DS* signals are expected. When MOTO* is high, indicating an Intel-style

interface, CS*, ALE, RD*, and WR* signals are expected.

pin should usually be tied high for Intel devices and tied low for Motorola

devices. SYNCMD puts the interface into the Synchronous Processor Interface

Mode. Motorola 68000 processors typically have SYNCMD tied high if MCLK is

connected to the MPU clock source; Intel 8051 processors have SYNCMD tied

low (see

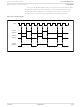

Table 2-7. Microprocessor Interface Operating Modes

Figure

process. The INTR* output pin is an active low, open-drain type output which

provides a common interrupt request for all eight framers and the LIU serial

interface.

registers (IER[7:0]), and an interrupt request register (IRR). Events such as alarm

status changes and sync signals are latched in ISR registers until read by the

microprocessor. Each ISR bit has a corresponding IER bit used to enable or

disable interrupt generation. If enabled, an ISR event is reported in the

appropriate IRR bit.

When MOTO* is low, indicating a Motorola-style interface, CS*, AS*, R/W*,

When MOTO* is high, the address lines are multiplexed with the data. This

Each framer includes interrupt status registers (ISR[7:0]), interrupt enable

MOTO*

0

0

1

1

2-28, Interrupt Generation Block Diagram, details the interrupt generation

Table

2-7).

SYNCMD

Conexant

0

1

0

1

Asynchronous Motorola, internal clock

Synchronous Motorola, external clock

Asynchronous Intel, internal clock

Synchronous Intel, external clock

Quad/x16/Octal—T1/E1/J1 Framers

Description

CX28394/28395/28398

100054E

Related parts for cx28394

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

ATM transmitter/receiver with UTOPIA interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Service SAR controller

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

CN8223EPFATM Transmitter/Receiver with UTOPIA Interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Embedded modem family

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Fully integrated T1/E1 framer and line interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Home Networking Physical Layer Device with Integrated Analog Front End Circuitry Data Sheet (Preliminary) CX82100-41Home Network Processor (HNP)

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

SmartV.XX Modem

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Multichannel synchronous communications controller

Manufacturer:

Conexant Systems, Inc.

Datasheet: