cx28394 Conexant Systems, Inc., cx28394 Datasheet - Page 115

cx28394

Manufacturer Part Number

cx28394

Description

Quad/x16/octal-t1/e1/j1 Framers

Manufacturer

Conexant Systems, Inc.

Datasheet

1.CX28394.pdf

(305 pages)

- Current page: 115 of 305

- Download datasheet (3Mb)

CX28394/28395/28398

Quad/x16/Octal—T1/E1/J1 Framers

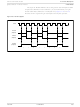

Figure 2-28. Interrupt Generation Block Diagram

100054E

INTR*

NOTE(S):

(1)

In CX28395, INTR1* is provided for Framers 1-8, and INTR2* is provided for Framers 9-16.

Register

MIR

the master interrupt enable register [MIE; addr 01E] and are routed to the master

interrupt register [MIR; addr 01D]. MIE provides a convenient location to enable

or disable interrupts for an entire framer. The serial done bit [SER_STAT;

addr 024] is gated with the serial interrupt enable bit [SER_CONFIG; addr 025]

to produce an additional interrupt request. Finally, MIR bits and the LIU serial

interface interrupt request are combined to generate a single interrupt request

signal on the INTR* pin.

The IRR bits from each framer are gated with the corresponding enable bit in

Using these registers, the microprocessor can process interrupts as follows:

Interrupt service routine

1.

2.

3.

4.

SER_DONE

SER_IER

Read MIR and SER_STAT registers to determine which framer or framers

caused the interrupt or whether LIU serial operation occurred.

For each interrupting framer, read IRR to determine which ISR contains

the interrupt event or events.

Read the ISR and mask the interrupt event bit using the corresponding IER

to determine which event or events caused the interrupt.

Enter the appropriate service routine.

Register

MIE

Framer 8

Framer 7

Conexant

Framer 6

Framer 5

Framer 4

Framer 3

Framer 2

Framer 1

Register

IRR

2.5 Microprocessor Interface

2.0 Circuit Description

Registers

Latches

ISR

IER

Events

2-57

Related parts for cx28394

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

ATM transmitter/receiver with UTOPIA interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Service SAR controller

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

CN8223EPFATM Transmitter/Receiver with UTOPIA Interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Embedded modem family

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Fully integrated T1/E1 framer and line interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Home Networking Physical Layer Device with Integrated Analog Front End Circuitry Data Sheet (Preliminary) CX82100-41Home Network Processor (HNP)

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

SmartV.XX Modem

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Multichannel synchronous communications controller

Manufacturer:

Conexant Systems, Inc.

Datasheet: