cx28394 Conexant Systems, Inc., cx28394 Datasheet - Page 116

cx28394

Manufacturer Part Number

cx28394

Description

Quad/x16/octal-t1/e1/j1 Framers

Manufacturer

Conexant Systems, Inc.

Datasheet

1.CX28394.pdf

(305 pages)

- Current page: 116 of 305

- Download datasheet (3Mb)

2.0 Circuit Description

2.5 Microprocessor Interface

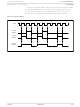

2.5.4 Device Reset

2-58

The device contains four reset methods:

configuration registers set to default values as shown in

In all reset methods, SYSCKI must be present during the reset process for proper

operation. MCLK (internal or external) performs the actual register initialization.

Therefore, if the SYNCMD pin is connected high to enable external MCLK, the

external MCLK must be applied during reset, and if the SYNCMD pin is low

during reset, the internal clock (33 MHz) is used and external MCLK is not

required. After hardware reset, software reset, or internal power-on reset, the

microprocessor must initialize the configuration registers to the desired state.

reached approximately 2.0 V, the internal reset process begins and continues for

100 SYSCKI cycles if SYSCKI is applied. If SYSCKI is not present, the device

remains in the reset state and does not terminate until detecting 100 SYSCKI

cycles. GRESET or RESET can be monitored to determine when POR is

complete. MCLK (internal or external) must be present during the POR

concurrent with SYSCKI to allow register initialization.

minimum of 4 µs. If SYNCMD is high (using external MCLK), external MCLK

must be present while RST* is low to allow register initialization. After RST* is

deactivated, the internal reset process continues for 5 µs and register access

should be avoided. GRESET can be monitored to determine when the reset

process is complete.

1.

2.

3.

4.

All four methods result in device outputs placed in a high-impedance state and

An internal POR process is initiated during power-up. When VDD has

Hardware reset is initiated by bringing the RST* pin active (low) for a

Internal Power-On Reset (POR),

Hardware Reset which uses the RST* pin,

Global Software Reset which uses the GRESET bit in register FCR [addr

080], and

Software Reset which uses the RESET bit in register CR0 [addr 001].

Conexant

Quad/x16/Octal—T1/E1/J1 Framers

CX28394/28395/28398

Table 3-4, Address

100054E

Map.

Related parts for cx28394

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Bluetooth RF Transceiver

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

ATM transmitter/receiver with UTOPIA interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Service SAR controller

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

CN8223EPFATM Transmitter/Receiver with UTOPIA Interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Embedded modem family

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Fully integrated T1/E1 framer and line interface

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Home Networking Physical Layer Device with Integrated Analog Front End Circuitry Data Sheet (Preliminary) CX82100-41Home Network Processor (HNP)

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Flicker-free video encoder

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

SmartV.XX Modem

Manufacturer:

Conexant Systems, Inc.

Datasheet:

Part Number:

Description:

Multichannel synchronous communications controller

Manufacturer:

Conexant Systems, Inc.

Datasheet: