DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 214

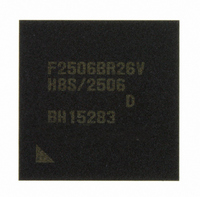

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 214 of 980

- Download datasheet (6Mb)

Section 7 Bus Controller

• The bus mastership is transferred at a break between bus cycles. However, if a bus cycle is

• If the CPU is in sleep mode, it transfers the bus mastership immediately.

DTC: The DTC sends the bus arbiter a request for the bus mastership when an activation request

is generated.

The DTC can release the bus mastership after a vector read, a register information read (3 states),

a single data transfer, or a register information write (3 states). It does not release the bus

mastership during a register information read (3 states), a single data transfer, or a register

information write (3 states).

7.10.3

External bus mastership release can be performed on completion of an external bus cycle. The CS

signal remains low until the end of the external bus cycle. Therefore, when external bus

mastership release is performed, the CS signal may change from the low level to the high-

impedance state.

7.11

In a power-on reset, this LSI, including the bus controller, enters the reset state at that point, and

an executing bus cycle is discontinued.

In a manual reset, the bus controller’s registers and internal state are maintained, and an executing

external bus cycle is completed. In this case, WAIT input is ignored and write data is not

guaranteed.

Rev. 6.00 Sep. 24, 2009 Page 166 of 928

REJ09B0099-0600

executed in discrete operations, as in the case of a longword-size access, the bus mastership is

not transferred between the operations.

Usage Note for External Bus Mastership Release

Resets and the Bus Controller

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: