DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 644

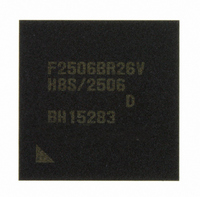

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 644 of 980

- Download datasheet (6Mb)

Section 17 IEBus™ Controller (IEB) [H8S/2552 Group]

17.4.3

This section shows an example of performing a master reception using the DTC after slave

reception.

(1)

(a) Setting the IEBus Control Register (IECTR)

(b) Setting the IEBus Master Unit Address Registers 1 and 2 (IEAR1 and IEAR2)

(c) Setting the IEBus Slave Address Setting Registers 1 and 2 (IESA1 and IESA2)

(d) Setting the IEBus Master Control Register (IEMCR)

(e) Setting the IEBus Receive Interrupt Enable Register (IEIER)

The above registers can be specified in any order. (The register specification order does not affect

the IEB operation.)

(2)

1. Set the start address of the RAM which stores the register information necessary for the DTC

2. Set the following data from the start address of the RAM.

3. Set bit DTCEG6 in the DTC enabler register G (DTCERG), and enable the RxRDY interrupt

Rev. 6.00 Sep. 24, 2009 Page 596 of 928

REJ09B0099-0600

Enable the IEBus pins, select the signal polarity, and select a clock supplied to the IEB. Set the

RE bit to 1 to perform reception. The LUEE bit does not need to be specified.

Specify the master unit address and specify the communications mode in IEAR1. Compare

with the slave address in the communications frame and receive the frame if matched.

Specify the communications destination slave unit address.

Select broadcast/normal communications, specify the number of retransfer counts at arbitration

loss, and specify the control bits.

Enable the RxRDY (IERxI), RxS, RxF, and RxE (IERSI) interrupts.

transfer in the vector address (H'000004D2) to be accessed when a DTC transfer request is

generated.

⎯ Transfer source address (SAR): Address (H'FFF80D) of the IEBus receive buffer register

⎯ Transfer destination address (DAR): Start address of the RAM which stores data to be

⎯ Transfer count (CRA): Maximum number of transfer bytes in one frame in the transfer

(IERxI).

IEB Initialization

DTC Initialization

(IERBR).

received from the data field.

mode.

Master Reception

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: