DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 833

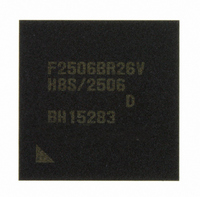

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 833 of 980

- Download datasheet (6Mb)

4. The clock pulse generator stops, and the setting for the STC1 and STC0 bits becomes valid.

5. Software standby mode or watch mode is exited, and the transition time set by the STS2 to

6. After the set transition time is elapsed, this LSI resumes operation with the changed

When the STCS bit is set to 1, after rewriting the STC1 and STC0 bits, this LSI operates with the

changed multiplication ratio.

21.4

The medium-speed clock divider divides the system clock to generate φ/2, φ/4, φ/8, φ/16, and

φ/32.

21.5

The bus master clock selection circuit selects the clock supplied to the bus master by setting the

SCK2 to SCK0 bits in SCKCR. The bus master clock can be selected from system clock (φ), or

medium-speed clocks (φ/2, φ/4, φ/8, φ/16, and φ/32).

21.6

When using the IEBus*

18 MHz, 18.87 MHz, 24 MHz, or 25.16 MHz.

When the IEBus*

used.

Notes: 1. The IEBus is supported only by the H8S/2552 Group.

STS0 bits is ensured.

multiplication ratio.

2. System clock frequency up to 20 MHz is supported by the H8S/2556 Group.

Medium-Speed Clock Divider

Bus Master Clock Selection Circuit

System Clock with IEBus

1

is not used, any system clock frequency between 8 MHz and 26 MHz*

1

, the system clock should be set with one of 12 MHz, 12.58 MHz,

Rev. 6.00 Sep. 24, 2009 Page 785 of 928

Section 21 Clock Pulse Generator

REJ09B0099-0600

2

can be

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: