DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 443

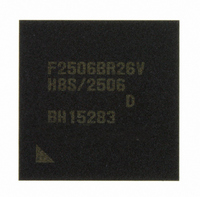

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 443 of 980

- Download datasheet (6Mb)

This LSI has five independent serial communication interface (SCI) channels. The SCI can handle

both asynchronous and clocked synchronous serial communication. In asynchronous mode, serial

data communication can be carried out using standard asynchronous communication chips such as

a Universal Asynchronous Receiver/Transmitter (UART) or an Asynchronous Communication

Interface Adapter (ACIA). In asynchronous mode, a function is also provided for serial

communication between multiple processors (multiprocessor communication function). The SCI

also supports an IC card (Smart Card) interface conforming to ISO/IEC 7816-3 (Identification

Card) as an extension function in clocked synchronous serial communication mode.

13.1

• Choice of asynchronous or clocked synchronous serial communication mode

• Full-duplex communication capability

• On-chip baud rate generator allows any bit rate to be selected

• Choice of LSB-first or MSB-first transfer (except in the case of asynchronous mode 7-bit data)

• Four interrupt sources

• Module stop mode can be set

Asynchronous mode

• Data length: 7 or 8 bits

• Stop bit length: 1 or 2 bits

• Parity: Even, odd, or none

• Receive error detection: Parity, overrun, and framing errors

(Because the same pin is used as the clock input/output pin for channel 1 and channel 4, these

clocks cannot be output at the same time.)

The transmitter and receiver are mutually independent, enabling transmission and reception to

be executed simultaneously.

The double-buffering configuration is adopted in both the transmitter and the receiver,

enabling continuous transmission and continuous reception of serial data.

External clock can be selected as a transfer clock source (except in Smart Card interface mode)

Transmit-end, transmit-data-empty, receive-data-full, and receive error — that can issue

requests.

The transmit-data-empty and receive-data-full interrupts can be used to activate the data

transfer controller (DTC).

Section 13 Serial Communication Interface (SCI)

Features

Section 13 Serial Communication Interface (SCI)

Rev. 6.00 Sep. 24, 2009 Page 395 of 928

REJ09B0099-0600

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: