DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 766

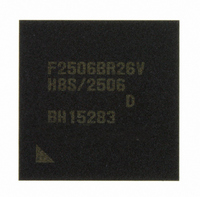

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 766 of 980

- Download datasheet (6Mb)

Section 20 Flash Memory

20.4.4

In the descriptions in the previous section, the programming/erasing procedure programs and

storable areas for program data are assumed to be in the on-chip RAM. However, the program and

the data can be stored in and executed from other areas, such as part of flash memory which is not

to be programmed or erased, or somewhere in the external address space.

(1)

1. The on-chip programming/erasing program is downloaded from the address in the on-chip

2. The on-chip programming/erasing program will use 128 bytes as a stack. So, make sure that

3. Download by setting the SCO bit to 1 will lead to switching of the MAT. If, therefore, this

4. The flash memory is accessible until the start of programming or erasing, that is, until the

5. The flash memory is not accessible during programming/erasing operations, therefore, the

6. After programming/erasing, the flash memory should be inhibited until FKEY is cleared.

7. Switching of the MATs by FMATS should be needed when programming/erasing of the user

8. When the data storable area indicated by programming parameter FMPDR is within the flash

Rev. 6.00 Sep. 24, 2009 Page 718 of 928

REJ09B0099-0600

RAM specified by FTDAR, therefore, this area is not available for use.

this area is secured.

operation is used, it should be executed from the on-chip RAM.

result of downloading has been determined. When in single-chip mode in which the external

address space is not accessible, the required procedure programs, NMI handling vector, NMI

handler, and user branch program should be transferred to the on-chip RAM before

programming/erasing of the flash memory starts.

operation program is downloaded to the on-chip RAM to be executed. The NMI-handling

vector and programs such as that which activate the operation program, and NMI handler

should thus be stored in on-chip memory other than flash memory or the external address

space.

The reset state (RES = 0) must be in place for more than 100 μs when the LSI mode is changed

to reset on completion of a programming/erasing operation.

Transitions to the reset state, and hardware standby mode are inhibited during

programming/erasing. When the reset signal is accidentally input to the chip, a longer period in

the reset state than usual (100 μs) is needed before the reset signal is released.

MAT is operated in user-boot mode. The program which switches the MATs should be

executed from the on-chip RAM. See section 20.7, Switching between User MAT and User

Boot MAT. Please make sure you know which MAT is selected when switching between

them.

memory area, an error will occur even when the data stored is normal. Therefore, the data

Conditions that Apply to Programming/Erasing

Procedure Program and Storable Area for Programming Data

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: