HD6433044 Hitachi Semiconductor, HD6433044 Datasheet - Page 531

HD6433044

Manufacturer Part Number

HD6433044

Description

(HD64 Series) Hitachi Single-Chip Microcomputer

Manufacturer

Hitachi Semiconductor

Datasheet

1.HD6433044.pdf

(867 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

HD6433044A00FV

Manufacturer:

HITACHI/日立

Quantity:

20 000

Company:

Part Number:

HD6433044F16

Manufacturer:

HITACHI

Quantity:

5 530

Company:

Part Number:

HD6433044F16

Manufacturer:

IDT

Quantity:

3 198

Company:

Part Number:

HD6433044F16

Manufacturer:

HITACHI

Quantity:

648

Part Number:

HD6433044F16A00

Manufacturer:

HITACHI/日立

Quantity:

20 000

Company:

Part Number:

HD6433044F18

Manufacturer:

HITACHI

Quantity:

5 530

Part Number:

HD6433044F18

Manufacturer:

HITACHI/日立

Quantity:

20 000

Company:

Part Number:

HD6433044F18M08

Manufacturer:

TI

Quantity:

403

Part Number:

HD6433044F18M08

Manufacturer:

HITACHI/日立

Quantity:

20 000

- Current page: 531 of 867

- Download datasheet (3Mb)

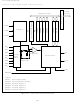

Retransmission: Retransmission is described below for the separate cases of transmit mode and

receive mode.

Retransmission when SCI is in Receive Mode (See Figure 14-11):

(1) The SCI checks the received parity bit. If it detects an error, it automatically sets the PER flag

(2) The RDRF bit in SSR is not set to 1 for the error frame.

(3) If an error is not detected when the parity bit is checked, the PER flag is not set in SSR.

(4) If an error is not detected when the parity bit is checked, receiving operations are assumed to

(5) When a normal frame is received, at the error signal transmit timing, the data pin is held in

to 1. If the RIE bit in SCR is set to the enable state, an ERI interrupt is requested. The PER

flag should be cleared to 0 in SSR before the next parity bit sampling timing.

have ended normally, and the RDRF bit is automatically set to 1 in SSR. If the RIE bit in SCR

is set to the enable state, an RXI interrupt is requested. If RXI is enabled as a DMA transfer

activation source, the RDR contents can be read automatically. When the DMAC reads the

RDR data, it automatically clears RDRF to 0.

the high-impedance state.

RDRF

PER

Ds D0 D1 D2 D3 D4 D5 D6 D7 Dp

Figure 14-11 Retransmission in SCI Receive Mode

Frame n

DE

(2)

(1)

Ds D0 D1 D2 D3 D4 D5 D6 D7 Dp

521

Retransmitted frame

(DE)

(4)

(3)

Ds

D0 D1 D2 D3 D4

Frame n + 1

Related parts for HD6433044

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

HM628128LFP-10Hitachi Semiconductor [131072-word x 8-bit High Speed CMOS Static RAM]

Manufacturer:

HITACHI

Datasheet:

Part Number:

Description:

Silicon N-Channel Junction FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel Junction FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N-Channel MOS FET

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

GaAs HEMT

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N Channel MOS FET High Speed Power Switching

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N Channel MOS FET High Speed Power Switching

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N Channel MOS FET Low Frequency Power Switching

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N Channel MOS FET High Speed Switching

Manufacturer:

Hitachi Semiconductor

Datasheet:

Part Number:

Description:

Silicon N Channel MOS FET High Speed Switching

Manufacturer:

Hitachi Semiconductor

Datasheet: