R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1118

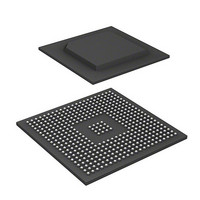

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1118 of 1694

- Download datasheet (9Mb)

21. Serial Communication Interface with FIFO (SCIF)

(1)

A fixed 8-bit data format is used. No parity bit can be added.

(2)

Either an internal clock generated by the on-chip baud rate generator or an external

synchronization clock input at the SCIF_SCK pin can be selected as the SCIF's serial clock,

according to the settings of the C/A bit in SCSMR and the CKE1 and CKE0 bits in SCSCR. For

details on SCIF clock source selection, see table 21.5.

When the SCIF is operated on an internal clock, the synchronization clock is output from the

SCIF_SCK pin. Eight synchronization clock pulses are output in the transfer of one character, and

when no transfer is performed, the clock is fixed high. When an internal clock is selected in a

receive operation only, as long as the RE bit in SCSCR is set to 1, clock pulses are output until the

number of receive data bytes in the receive FIFO data register reaches the receive trigger count.

(3)

Before transmitting and receiving data, it is necessary to clear the TE and RE bits in SCSCR to 0,

then initialize the SCIF as described below.

When changing the operating mode or transfer format, etc., the TE and RE bits must be cleared to

0 before making the change using the following procedure. When the TE bit is cleared to 0,

SCTSR is initialized. Note that clearing the RE bit to 0 does not initialize the RDF, PER, FER, or

ORER flag state or change the contents of SCFRDR.

Figure 21.16 shows a sample SCIF initialization flowchart.

Rev.1.00 Jan. 10, 2008 Page 1086 of 1658

REJ09B0261-0100

Data Transfer Format

Clock

SCIF Initialization (Clocked Synchronous Mode)

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: