R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1226

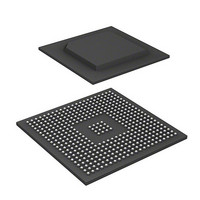

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1226 of 1694

- Download datasheet (9Mb)

24. Multimedia Card Interface (MMCIF)

24.3.8

CTOCR specifies the period to generate a timeout for the command response.

The counter (CTOUTC), to which the peripheral bus does not have access, counts the transfer

clock to monitor the command timeout. The initial value of CTOUTC is 0, and CTOUTC starts

counting the transfer clock from the start of command transmission. CTOUTC is cleared and stops

counting the transfer clock when command response reception has been completed, or when the

command sequence has been aborted by setting the CMDOFF bit to 1.

When the command response cannot be received, CTOUTC continues counting the transfer clock,

and enters the command timeout error state when the number of transfer clock cycles reaches the

number specified in CTOCR. When the CTERIE bit in INTCR1 is set to 1, the CTERI flag in

INTSTR1 is set. As CTOUTC continues counting transfer clock, the CTERI flag setting condition

is repeatedly generated. To perform command timeout error handling, the command sequence

should be aborted by setting the CMDOFF bit to 1, and then the CTERI flag should be cleared to

prevent extra-interrupt generation.

Note: If R2 response (17-byte command response) is requested and CTSEL0 is cleared to 0, a

Rev.1.00 Jan. 10, 2008 Page 1194 of 1658

REJ09B0261-0100

Bit

7 to 1

0

timeout is generated during response reception. Therefore, set CTSEL0 to 1.

Command Timeout Control Register (CTOCR)

Bit Name

—

CTSEL0

Initial value:

Initial

Value

All 0

1

R/W:

Bit:

⎯

R

7

0

R/W

R

R/W

⎯

6

0

R

Description

Reserved

These bits are always read as 0. The write value should

always be 0.

Command Timeout Select

0: 128 transfer clock cycles from command

1: 256 transfer clock cycles from command

Transfer clock: MMCCLK

⎯

R

5

0

transmission completion to response reception

completion

transmission completion to response reception

completion

⎯

4

0

R

⎯

R

0

3

⎯

2

0

R

⎯

R

1

0

CTSEL0

R/W

0

1

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: