R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1344

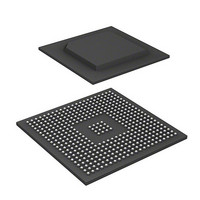

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1344 of 1694

- Download datasheet (9Mb)

26. Serial Sound Interface (SSI) Module

Note:

Rev.1.00 Jan. 10, 2008 Page 1312 of 1658

REJ09B0261-0100

Bit

1

0

*

These bits are readable/writable bits. If writing 0, these bits are initialized, although

writing 1 is ignored.

Bit Name

SWNO

IDST

Initial

Value

1

1

R/W

R

R

Description

Serial Word Number

The number indicates the current word number.

When TRMD = 0 (Receive Mode):

This bit indicates which system word the current data in

SSIRDR is. Regardless whether the data has been read

out from SSIRDR, when the data in SSIRDR is updated

by transfer from the shift register, this value will change.

When TRMD = 1 (Transmit Mode):

This bit indicates which system word should be written

in SSITDR. When data is copied to the shift register,

regardless whether the data is written in SSITDR, this

value will change.

Idle Mode Status Flag

Indicates that the serial bus activity has ceased.

This bit is cleared if EN = 1 and the serial bus is

currently active.

This bit can be set to 1 automatically under the

following conditions.

SSI = Serial bus master transmitter (SWSD = 1 and

TRMD = 1):

This bit is set to 1 if no more data has been written to

SSITDR and the current system word has been

completed. It can also be set to 1 when the EN bit has

been cleared and the data that has been written to

SSITDR is output on the serial data input/output pin

(SSI_SDATA), i.e., the serial data of the system word

length is output.

SSI = Serial bus master receiver (SWSD = 1 and TRMD

= 0):

This bit is set to 1 if the EN bit is cleared and the current

system word is completed.

SSI = slave transmitter/ receiver (SWSD = 0):

This bit is set to 1 if the EN bit is cleared and the current

system word is completed.

Note that when transmitting the data transmission in

slave mode, the WS signal should be input until

SSICR.IDST becomes 1 after SSICR.EN is cleared to

0.

Note: If the external device stops the serial bus clock

before the current system word is completed

then this bit will never be set.

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: