EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 291

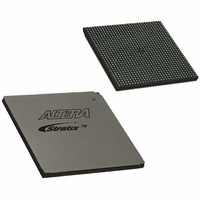

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 291 of 864

- Download datasheet (11Mb)

Stratix Device Handbook, Volume 1

Interconnect

IOE

J

JTAG

L

LAB

LUT

Altera Corporation

C4 Connections

DSP Block Interface to Interconnect

Left-Facing

LUT

M-RAM

R4 Connections

Internal Timing Microparameters

Boundary-Scan

Stratix JTAG

Control Signals

Wide Control Signals

Chain & Register Chain

Row I/O Block Connection to the

Row Pin

Signal Path through the I/O Block

SSTL-18

SSTL-2

SSTL-3 4–12,

Stratix

Supported I/O Standards

Transmitter Output Waveforms for Differ-

Column

Row Unit Interface to Interconnect

Register Length

Support

Instructions

Waveforms

Interface

Interconnects

I/O Standards

Interconnect

Configuration

ential I/O Standards

Interconnect

Input Delay Adders

Chain

4–12

IOE

4–11

3–1

M-RAM

3–4

2–40

3–2

Unit

2–5

4–13

2–18

2–15

in

3–3

2–17

2–6

2–106

2–42

Register

Bidirectional

2–110

4–5

2–8

to

Interface

2–123

4–6

4–67

Interconnect

4–29

2–72

Chain

2–108

2–41

I/O

to

M

Memory Architecture

Byte Enable for M4K

Byte Enable for M-RAM

External RAM Interfacing

M4K

M512

Memory Block Size

Memory Modes

M-RAM

RAM Block

Block

Block Internal Timing

RAM Block

Block Internal Timing

RAM Block

Block

Block Control Signals

Block Internal Timing

Combined

Microparameter

Microparameters

Configurations

Configurations

Control Signals

LAB Row Interface

Microparameter

Microparameters

Architecture

Configurations (Simple Dual-Port

Control Signals

LAB Row Interface

Configurations

Configurations

Microparameter

2–32

2–35

2–30

2–34

Byte

2–21

Descriptions

Port)

Port)

Descriptions

RAM)

Port)

Port)

Descriptions

2–26

Selection

2–27

2–37

2–31

2–31

2–34

2–35

2–115

2–27

2–33

2–29

(Simple

(Simple

4–31

(True

4–30

(True

2–33

2–30

4–24

4–24

4–25

for

Index–5

Dual-

Dual-

Dual-

Dual-

x144

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: