EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 495

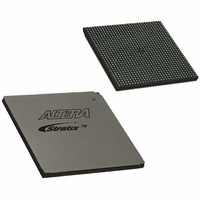

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 495 of 864

- Download datasheet (11Mb)

Figure 5–16. Fast PLL & Channel Layout in EP1S10, EP1S20 & EP1S25 Devices

Notes to

(1)

(2)

(3)

Altera Corporation

July 2005

Wire-bond packages only support up to 624 Mbps until characterization shows otherwise.

See

There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of

its bank quadrant (e.g., if PLL 2 clocks PLL 1’s channel region), those clocked channels support up to 840 Mbps.

Transmitter Channels (2)

Transmitter Channels (2)

Up to 20 Receiver and

Up to 20 Receiver and

Tables 5–10

Figure

Transmitter

Transmitter

Receiver

Receiver

5–16:

CLKIN

CLKIN

f

through

5–14

Fast PLL SERDES Channel Support

The Quartus II MegaWizard Plug-In Manager only allows you to

implement up to 20 receiver or 20 transmitter channels for each fast PLL.

These channels operate at up to 840 Mbps. For more information on

implementing more than 20 channels, see

receiver and transmitter channels are interleaved such that each I/O bank

on the left and right side of the device has one receiver channel and one

transmitter channel per row.

layout in EP1S10, EP1S20, and EP1S25 devices.

PLL and channel layout in EP1S30 to EP1S80 devices.

For more the number of channels in each device, see

5–14.

PLL 1

PLL 2

for the exact number of channels each package and device density supports.

Fast

Fast

(3)

High-Speed Differential I/O Interfaces in Stratix Devices

(3)

Figure 5–16

PLL 4

PLL 3

Stratix Device Handbook, Volume 2

Fast

Fast

shows the fast PLL and channel

“Fast PLLs” on page

Figure 5–17

Note (1)

Up to 20 Receiver and

Transmitter Channels (2)

Up to 20 Receiver and

Transmitter Channels (2)

Transmitter

Receiver

CLKIN

CLKIN

Transmitter

Receiver

Tables 5–10

shows the fast

5–52. The

through

5–23

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: